Hi,

This gate driver is used to drive a SiC MOSFET, FF23MR12W1M1P.

Could you please advise how to choose the capacitor and the resistor for the denaturation function? This capacitor is called CBLK and the resistor is R on Figure 16 (page 22) of the UCC21750 datasheet.

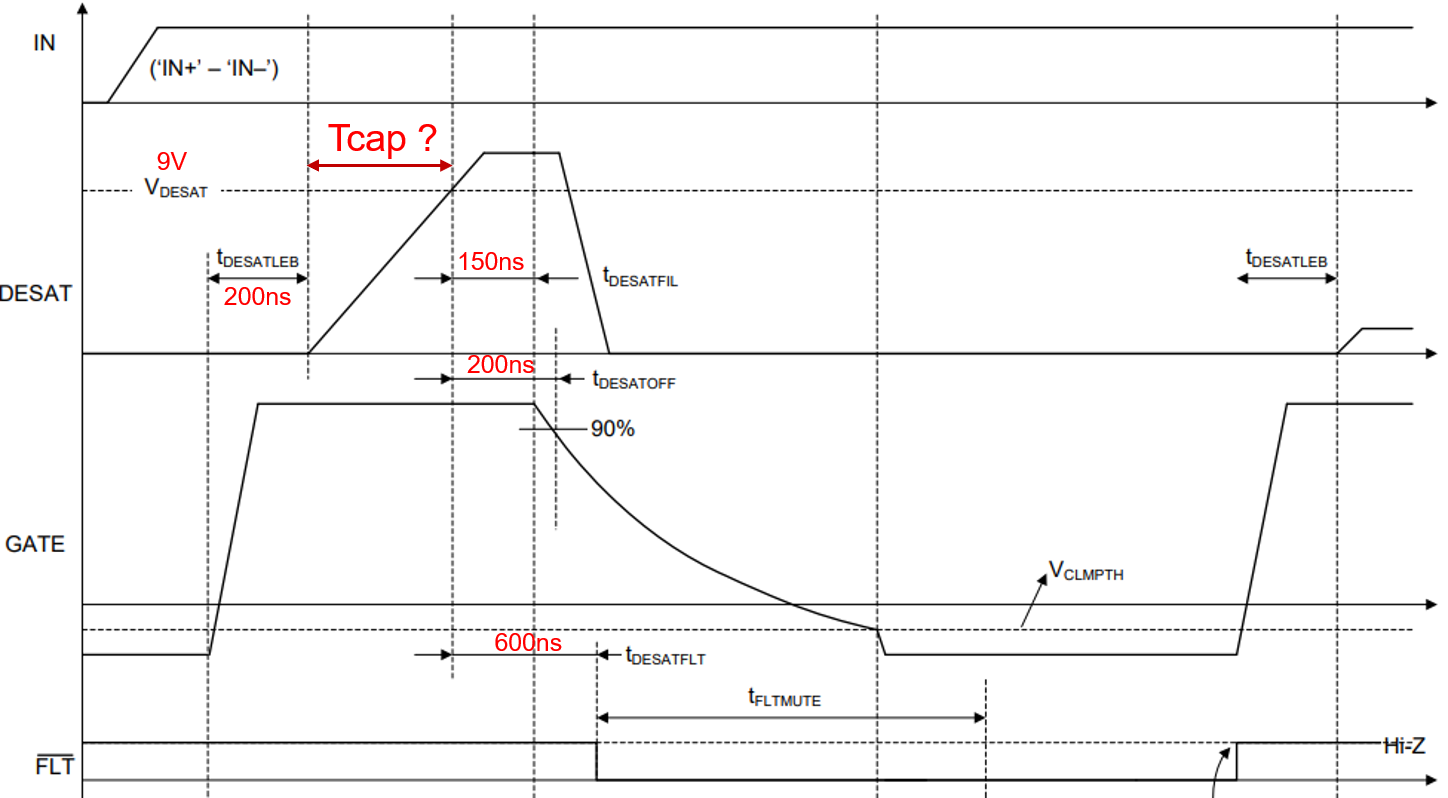

What is the best for Tcap in the following figure?

According to SLUA863A, Tcap=Vdesat*Cblk/Ichg=9V*Cblk/0.5mA; If Cblk=50pF, Tcap=900ns, so the total time from denaturation detection to fault is 900ns+600ns=1.5us. I am not sure if my calculation is right? Do I need to consider anything else?

then how to decide the R?

Another question is to help understand 6.5 power ratings on page 5.

Does this transmitter side mean the low voltage side (VCC side, pin 9-16) and the receiver side mean the high voltage side (VDD side, pin 1-8)?

Thanks,

Hongmei