Other Parts Discussed in Thread: LM5116

Hello,

We are using an LM5116 in a 48v to 28v (2A max) SMPS design. Under certain load conditions (~150-300mA) the circuit seems to become unstable and can often cause the low-side FET to fail. We suspected our layout might be the culprit, but we were able to reproduce the issue using the LM5116EVAL board. Any idea what may be causing this to occur?

Thanks....Alan

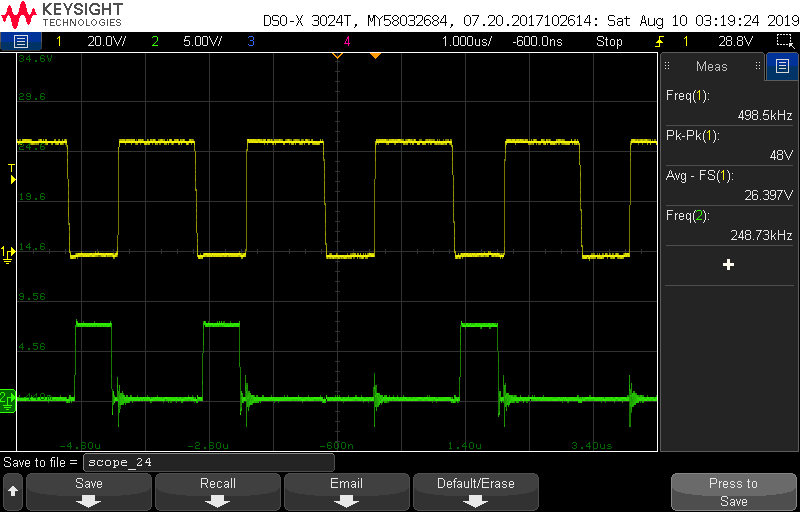

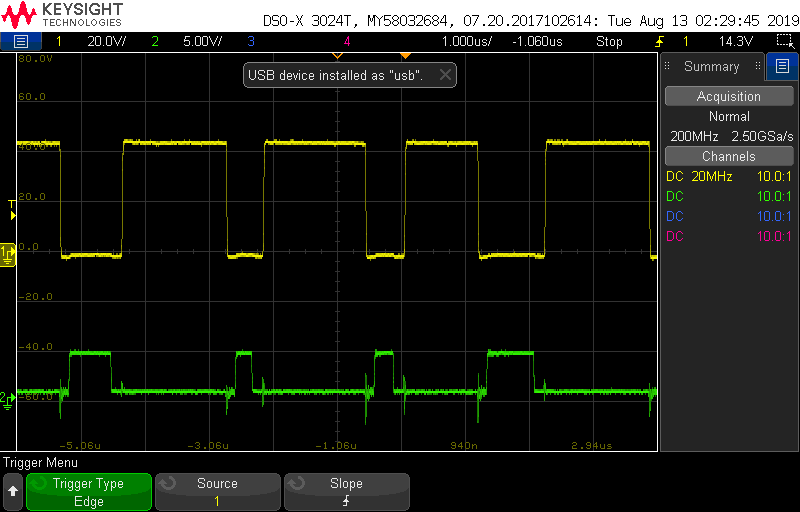

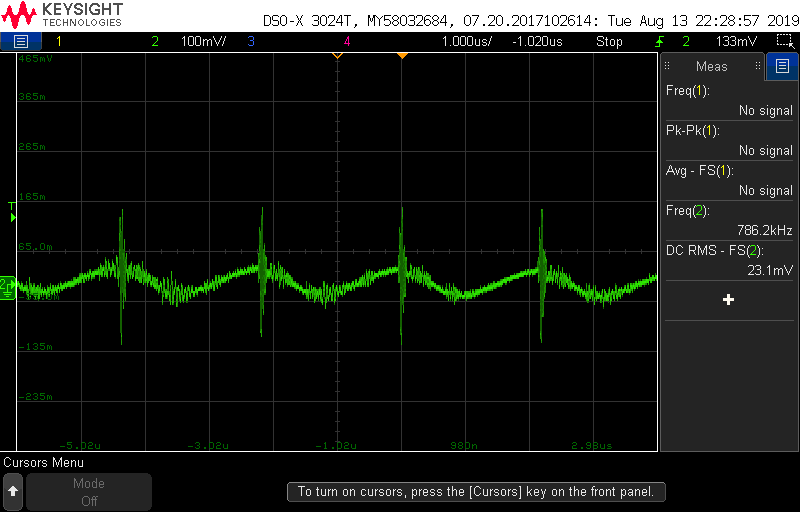

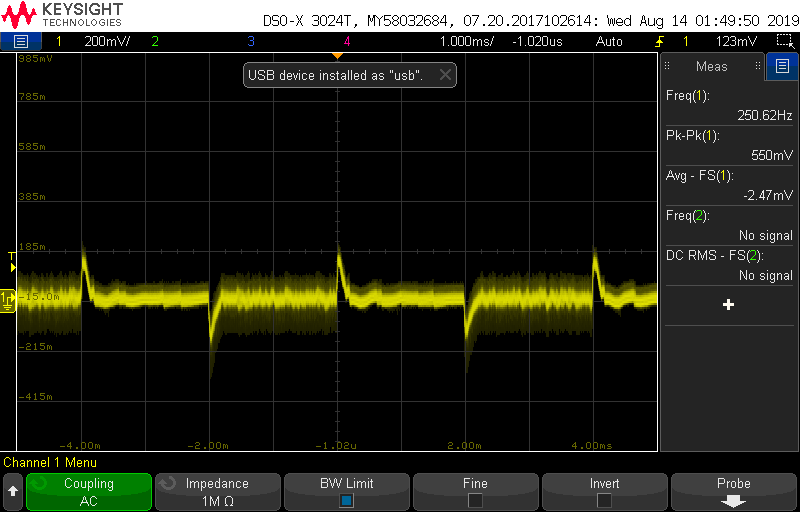

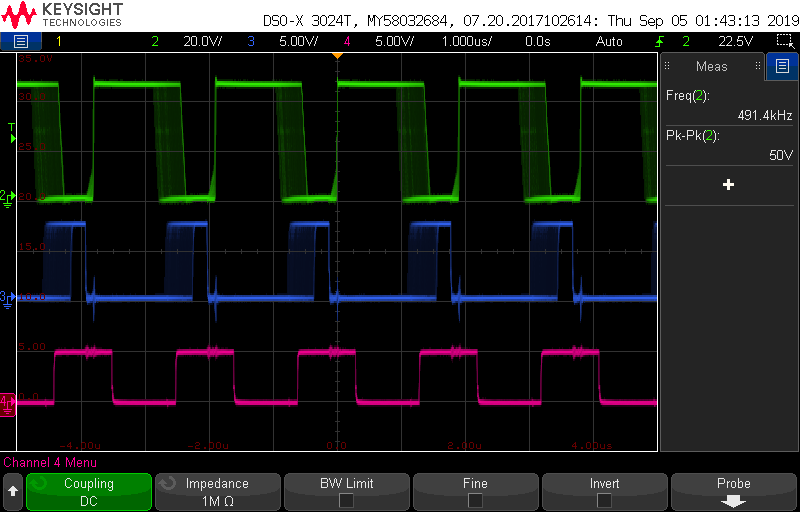

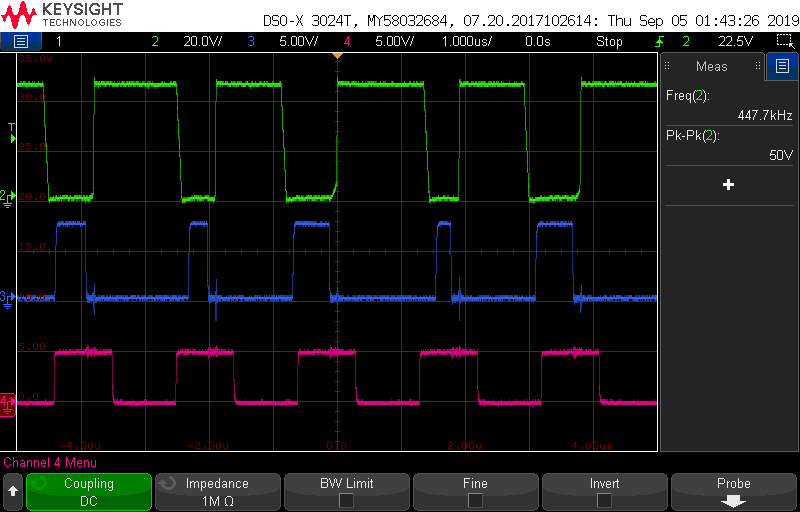

Yellow: Inductor input voltage

Green: Lower FET gate drive