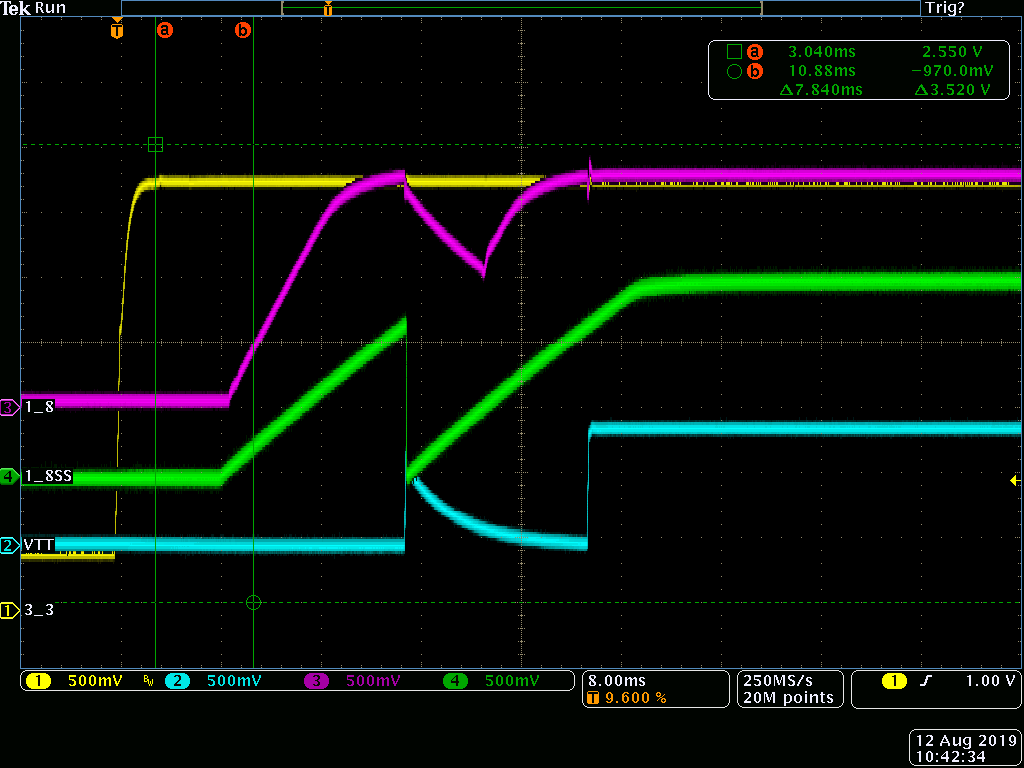

Hi Daniel, recently we've noticed an issue where our 1.8V regulator is entering a shutdown condition and restarting after a load on the 1.8V bus is enabled and the resulting inrush current causes the 1.8V supply to fall below regulation. The inrush lasts for about 80us and we've estimated that the peak current could be 8-9A (ignoring current ripple in the inductor) based on a simple Cdv/dt calculation. From the datasheet, this pulse could be exceeding the current limit for both the high and low side switches. The regulator is nominally switching at 500KHz, so I could expect up to 40 switching cycles to be operating in a current limited fashion. This pulse causes the 1.8V to immediately dip by about 10%. Then one of two things happen, either the regulator simply recovers back to 1.8V or it shuts off and restarts. My reading of the datasheet suggests that the only thing that would lead to this kind of shutdown is tripping the UVLO, the enable threshold or a thermal shutdown. Both the enable and Vin are at 3.3V. Thermal shutdown strikes me as unlikely given the short duration (80us). Is there anything outside of these conditions that can trigger a shutdown?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.