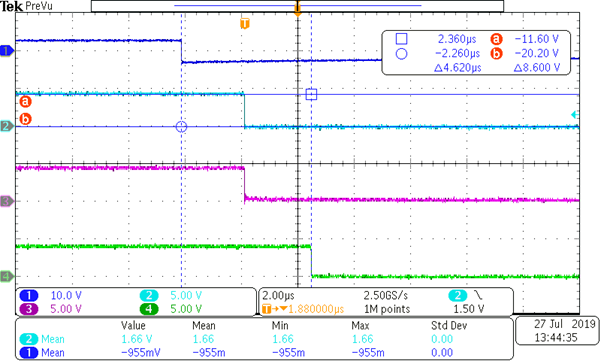

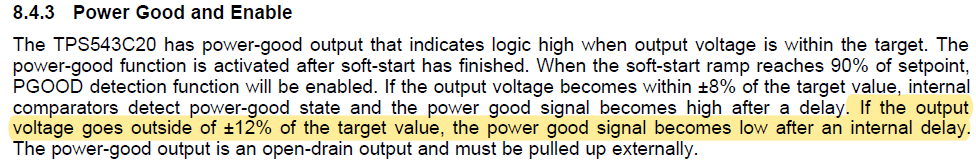

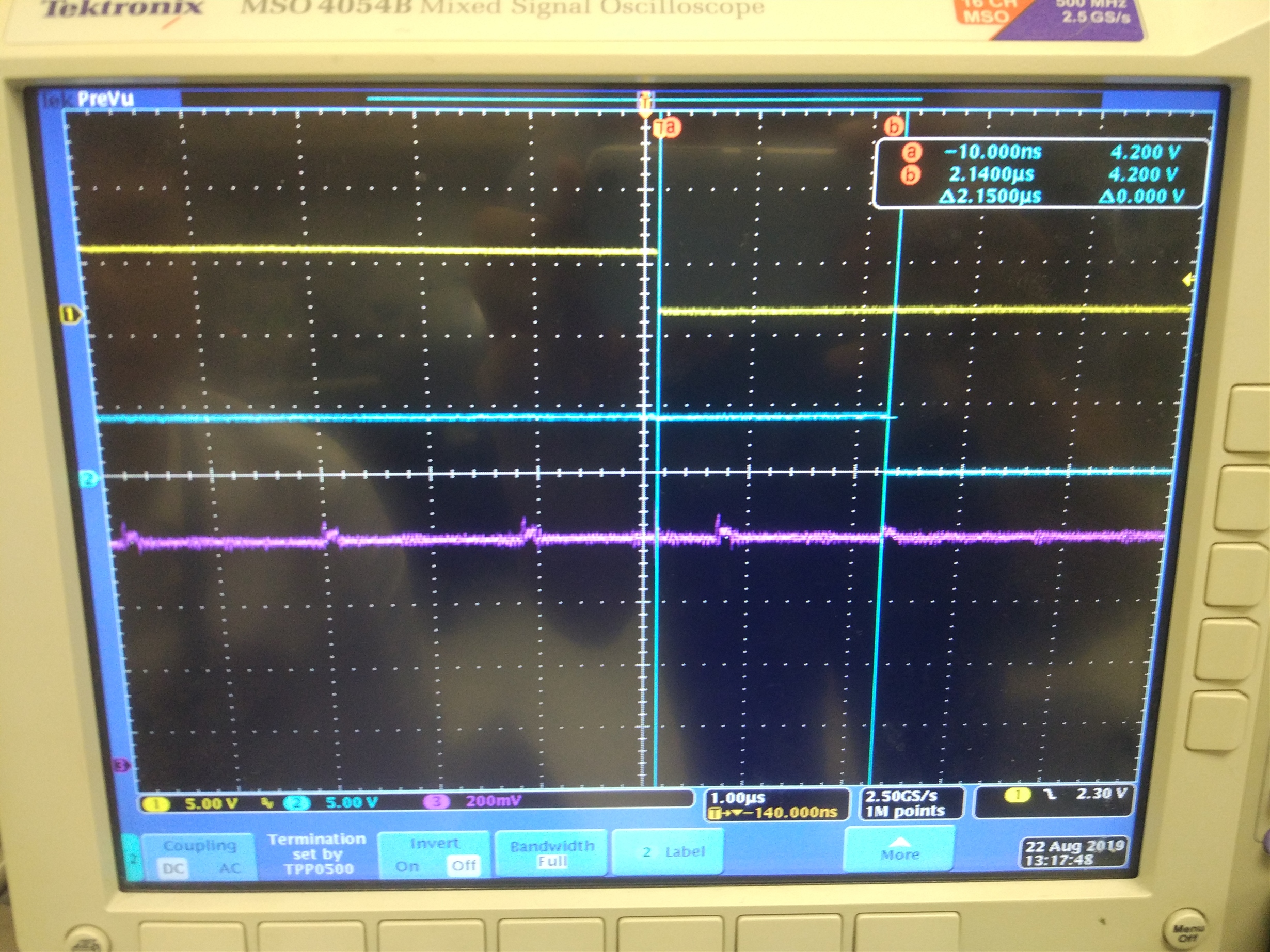

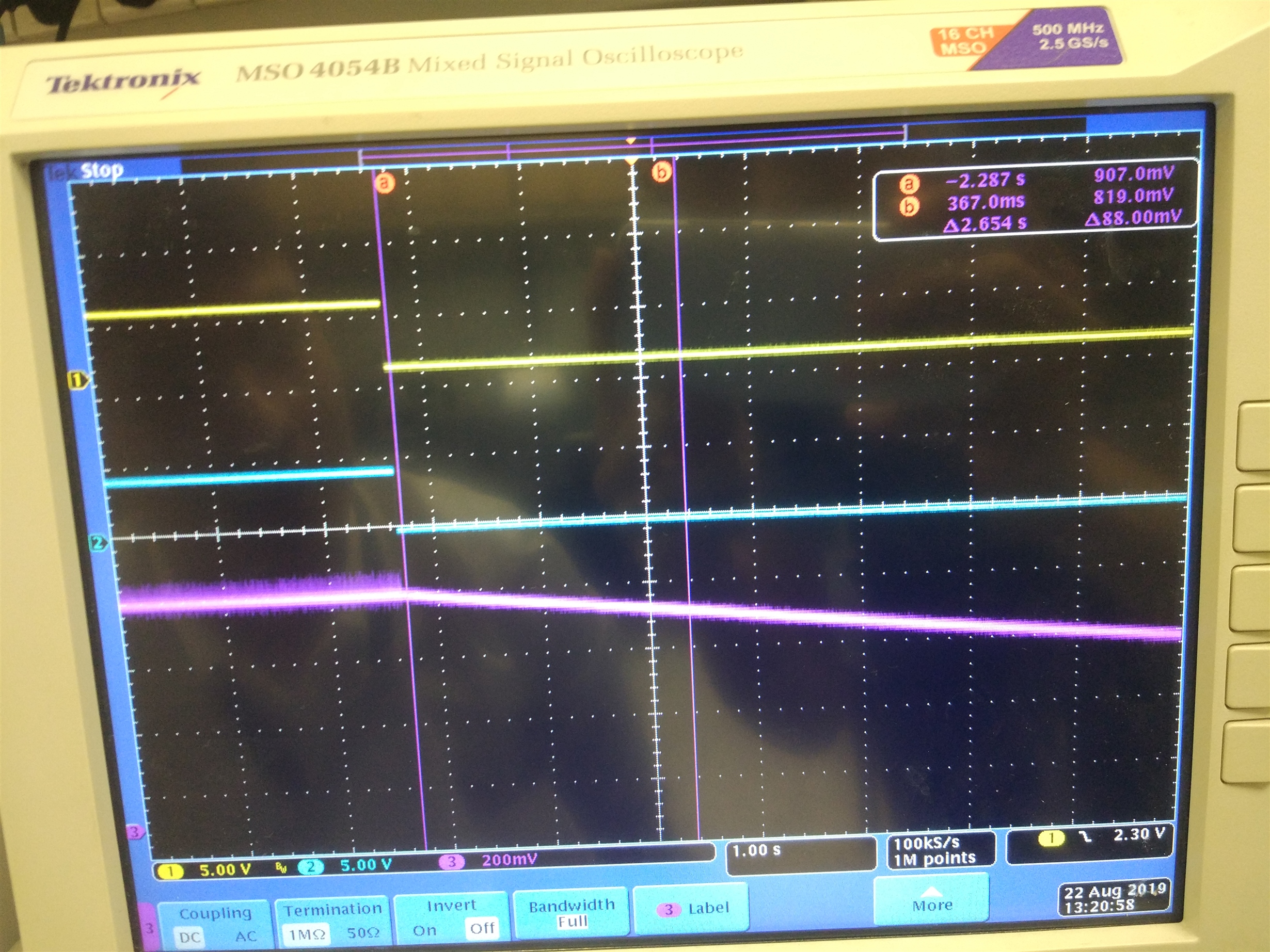

This is my test of power-off sequence on TPS543C20EVMs. 1 channel is EN of Module-A, 2 channel is PGD of Module-A, 3 channel is EN of Module-B, 4 channel is PGD of Module-B. When the EN of the module-A goes low, the PGD also goes low after a delay. Next, the EN of the module-B becomes a low level, and the PGD also becomes a low level after a delay. Time between EN disable of module-A and PGD response of module-B is 4.62us. However, in the datasheet, the delay for PGOOD coming out is 2us.

Test Conditions: 12V Vin, no load.

In my test, the output voltage needs more than 1 second to go outside the 12% of the target value under no load.

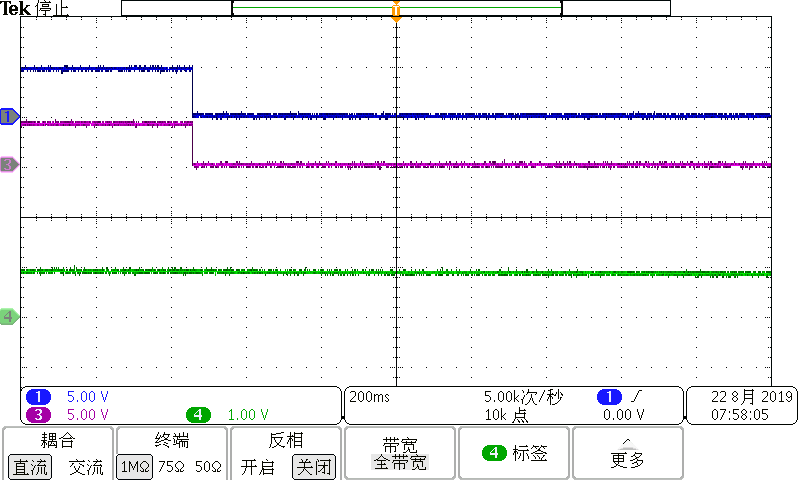

If the output voltage goes outside of ±12% of the target value, the power good signal becomes low after an internal delay. EN controls PGD when there is no load?