Dear Sir,

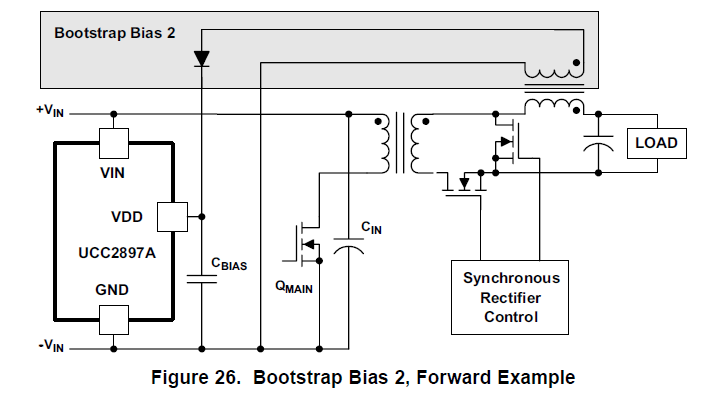

Our customer is using UCC2897A for 24V to 48V application, please see their schematic as below:

Currently. we got the power up fail issue and we figure out that PVDD power seems not stable enough and lead to power up fail . please see the waveform of PVDD vs Vout as below.

and here is the waveform for PL17 power input ans putout(measure both side if PL17, CH4 if the power in form transformer PT1 )

And we try disconnected the PL17(PVDD inductor) and give PVDD an external 12V power rail, and then the Vout 48 V will be power up ok. Therefore, we have tried to adjust the inductor and capacitance value (the red circle as the schematic as below)

and it seems that we couldn't stable the PVDD voltage.Also, we have tried to add a small load on output and it seems help stable the PVDD( it seems like that small load help UCC2897A get out of pluse skipping mode), Could you kinldy help us check the application and give us some advice for this issue? thanks in advance. also, we attach the transformer(PT1) and inductors(PL6, PL17) spec that they are currently use as your deference.

CEFD2513B(10393-T167)_RST-19-00465_1_Ext_20190611.pdf

Hope to heard form your soon.and if there is any question, please feel free to let me know

Alec