Hi,

I have four questions about BQ79606:

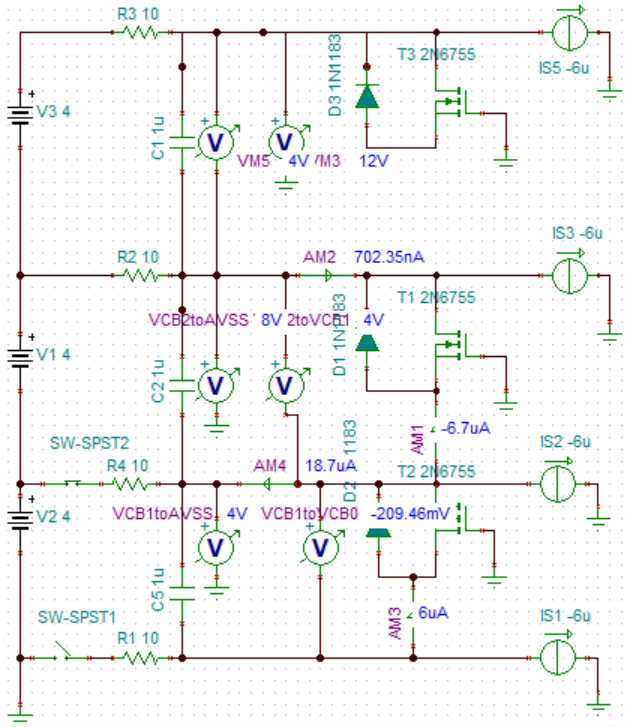

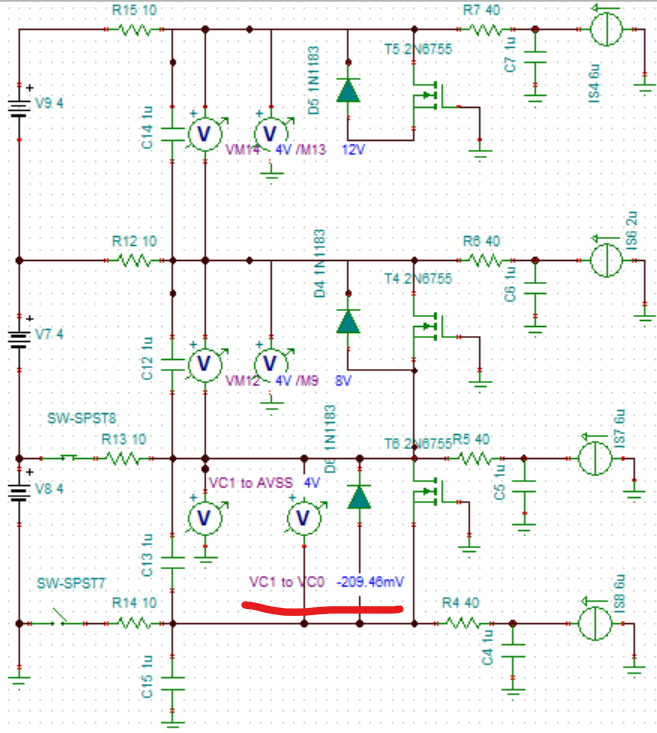

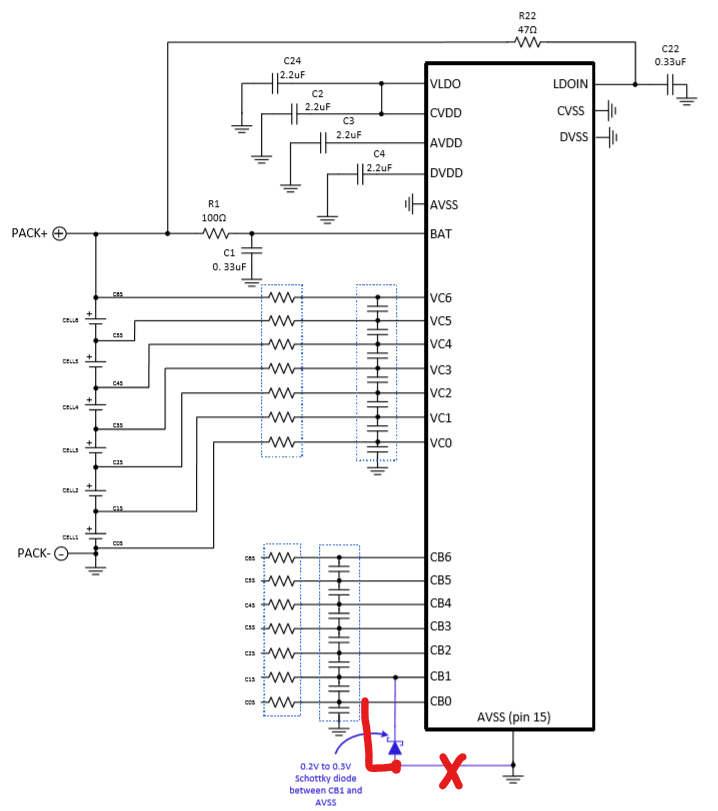

1.As the datasheet describes BQ79606 can pull down VC1-VC6/CB1-CB6 and pull up VC0/CB0 then read ADC value to do the open-wire detection. But could you tell me what exactly the ADC value difference will be between the normal connection case and open-wire case and why?

2.Why the VC0 and CB0 have to be pulled up rather than pulled down?

3."9.2.1.2.6 CB Input" section says "If a connection to cell1 negative terminal is open the IC bias current will flow through the CB1/VC1 pins and then to the cell2 negative module terminal, causing CB1 and VC1 pins to go below the minimum voltage recommended with respect to pin AVSS", where does this IC bias current comes from?

4.In the design recommendation, it says VC series resistance should be 4 times of CB resistance for the best hot-plug performance. Why this 4 times resistance setup can give me the best hot-plug performance?

Thank you for your reply!