Hi....

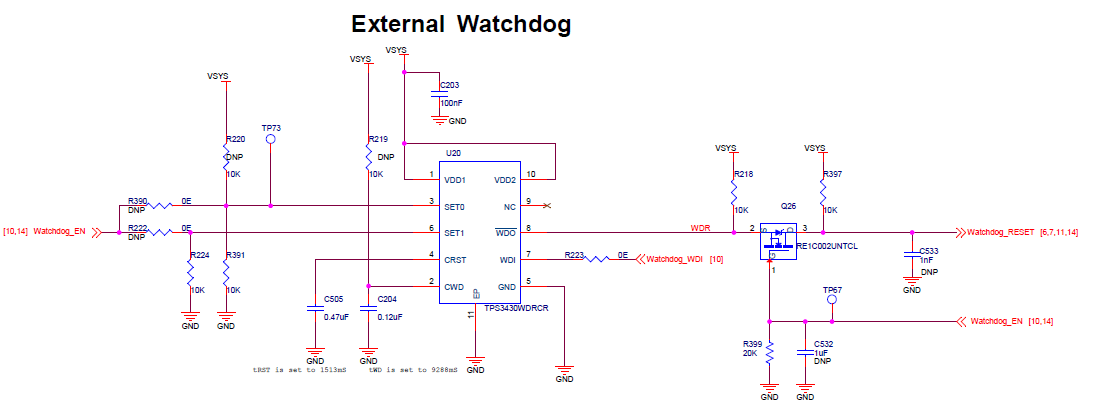

One of my customer is using TPS3430 in their project. Refer below schematic.

Customer has manufactured pilot batch of 100 boards and they have observed that most of the devices are rebooting at random time. During debug process they observed that watchdog output goes low even though WDI input is given to reset the counter.

They are using watchdog in a window mode. As per capacitor values of CRST and CWD pins; Trst time is approx. 1.5 sec and watchdog counter time is approx. 9 Sec. They initially provided WDI pulse at interval of 5 seconds and with that devices are rebooting then they reduced this time to 1.6 seconds but with that also device is rebooting, and device reboot is random in nature.

Please help resolving the issue, need details at what interval WDI input should be to avoid random reset?

Mitesh