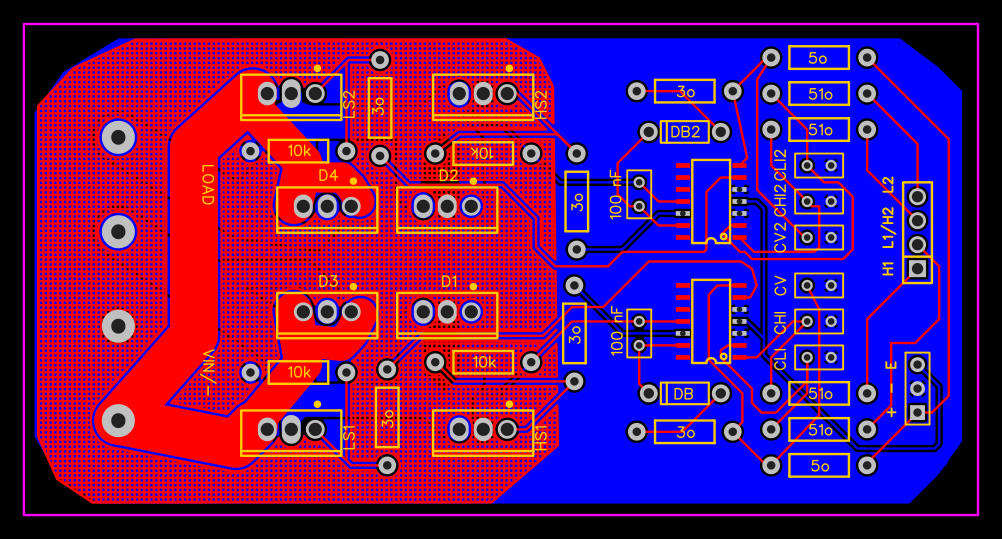

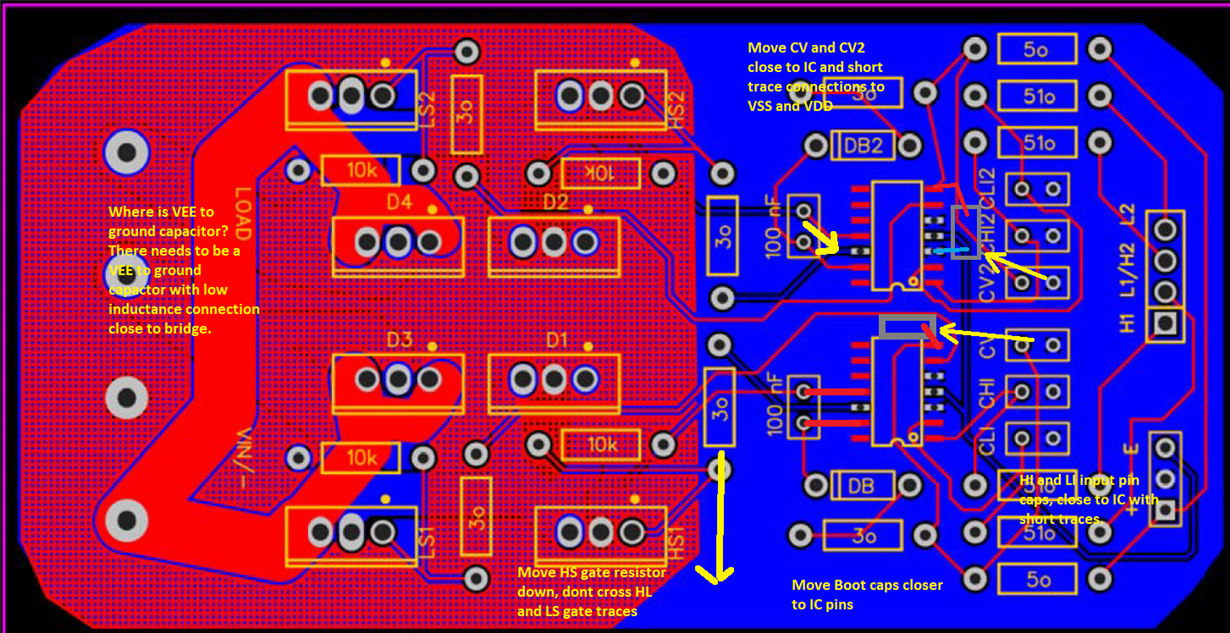

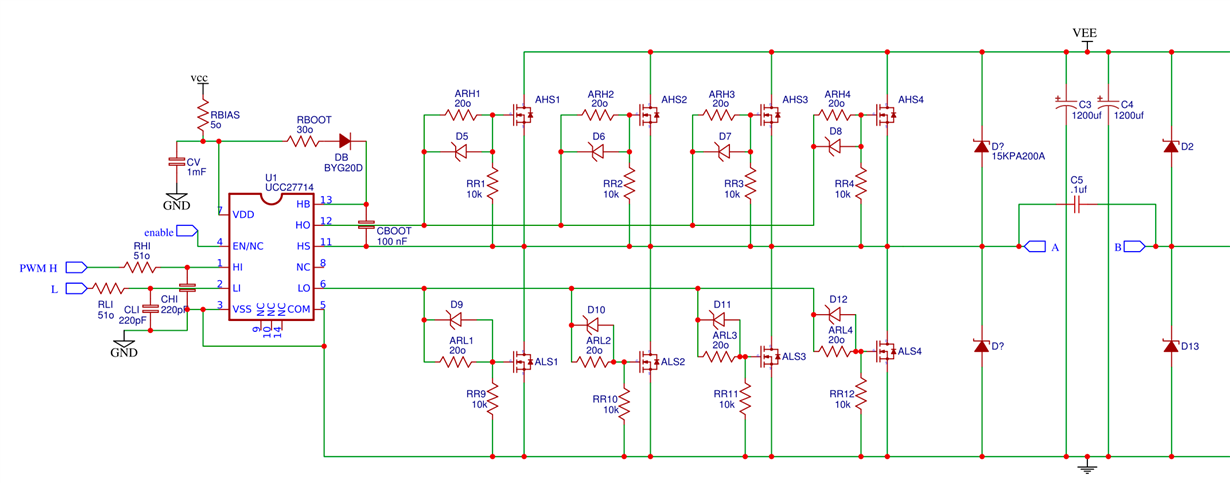

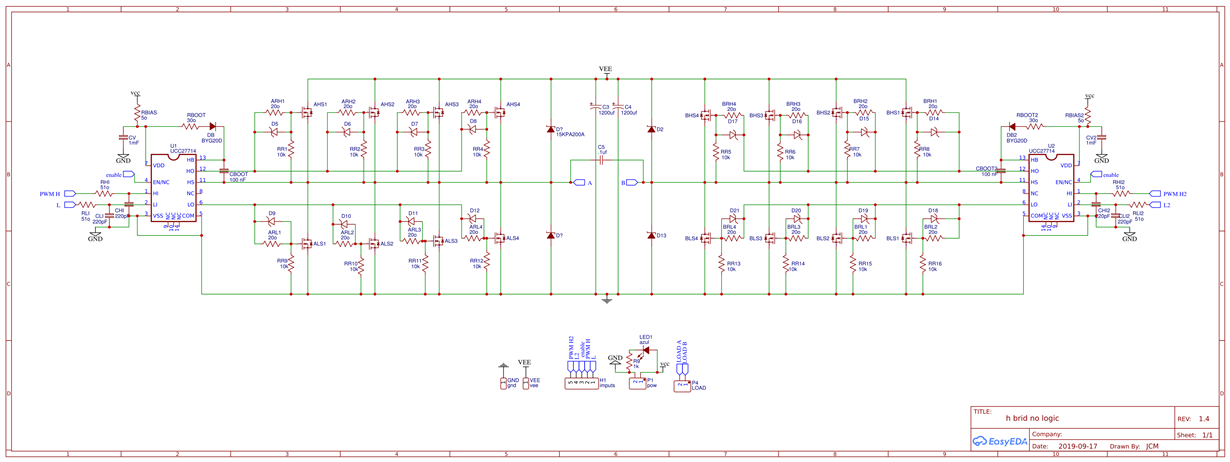

Hello! my name is jesus and recently I have been working on the design of a high current h bridge, I have to say that I am a little novice and would greatly appreciate any help. Make a pcb with the design that I show you here (200v h bridge) with an arduino doing the logic, to generate the pwm and the dir. I don't know what could have happened, since once I connected the bridge and turned on enable the bridge h burned. I also attached the design of the pcb (5x10 cm) and a photo of how the bridge h.

Please help me if you can!, I would be very grateful

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.