Hi All,

I have a large customer that needs help selecting a ceramic capacitor for the output.

Please see below.

Thanks,

Regards,

Joe

From Customer:

I’m having trouble merging the required output capacitor ESR with the real world capacitor ESR graph for the TI TPS7A7001DDA LDO

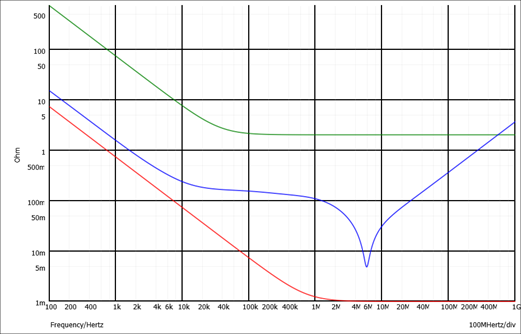

The TI part wants from 30m-ohm to 1 milli-ohm and a max of 1 ohm depending on load current(Figure 2 of datasheet). Since we may have one or two pieces of these regulators we cannot guarantee that we will be above 50 mA at all times especially during reset and boot so I look at the output capacitor graph and see that it wants 30milli-ohm of ESR at zero current.

But a typical ceramic capacitor has a ESR graph that is not flat depending on frequency so which frequency do I look at to see if we are meeting the required specification?

I looked at the TI eval board schematic for this part and it shows an 0805 10u X7R cap on the output. That has the same curve as well but does get above 1 ohm at about 400 Hz which breaks the max upper limit requirement. Our concern with 0805 capacitors is that they are hard to get as the market wants us to use 0402 or 0201 caps which make the ESR even lower not to mention voltage bias effects have an even lower actual capacitance but I’m more confused about the ESR graph and how to apply. I thinking 0603 might be a good compromise.

Some LDO’s say they are made for ceramic output caps and have a 0 ohm lower limit. Is the TPS7A7001DDA designed for ceramic output caps?

We have lots of downstream capacitors as well in the 10 uf range but there is some trace impedance to get to them and we have the ability to add ferrites in series if needed for noise and maybe to help isolate too much extra capacitor ESR from the LDO output.

Even the output ESR graph for the TPS79630 LDO isn’t clear on the lower limit. The graph stops at 10 milli-ohm. Not sure what happens below there.

We chose the TPS7A7001DDA for price reasons. If there is a better part that can get the heat out we would be happy to consider it. Our current can be quite high maybe 0.5 Amp depending on wifi transmit bursts for instance.

Can we use ceramic output capacitors for TPS7A7001 and what size and value is safe?