Hi, all!

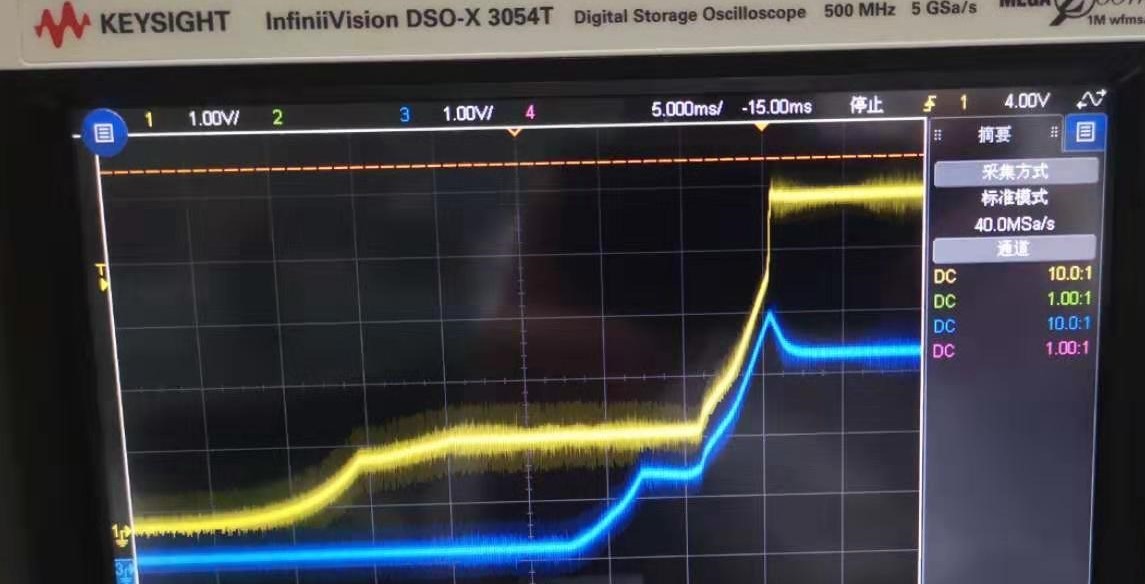

We used two LDOs, TPS70601DRBR, to provide the 3.3V and 1.2V supply for an Microsemi FPGA. The input of TPS70601DRBR is 5V. When we power up the circuit, it becomes so weird that the TPS70601DRBR which generates 1.2V sometimes cannot raise the output to the expected 1.2V. In this case, the output of the TPS70601DRBR is locked to 0.5V and therefore the FPGA fails to boot. However, this never happens at the 3.3V output TPS70601DRBR.

We have followed the recommended design demo in the datasheet of TPS70601DRBR and currently feel few clues of what is the reason for this problem. We guess if this problem results from few capacitors at the input end of this LDO, or the resistors labelled as R38A or R39A may have large current when the output of the LDO starts to climb.

We sincerely welcome any helps from TI.