Other Parts Discussed in Thread: UCC24650

Hello,

We are using is the UCC28730-Q1 PSR Flyback Controller. We are not using the associated UCC24650 wake up component because we do not have a light load application. We are using a schottky diode on the secondary side and all diodes are fast rectifiers. The transformer does not saturate. The load is a simple power resistor. Snubber have been added to reduce oscillations on Vds (due to the primary leakage inductance) and on the secondary side diode. We have checked all signals and they all looked quite good so that is why we feel like we are hitting a wall.

As said in the title, the main issue here is the efficiency. The current efficiency is staying between 55% and 58%, which is quite low for a flyback. Moreover, the controller is given with an average efficiency of 80%.

The only strange things we noticed are:

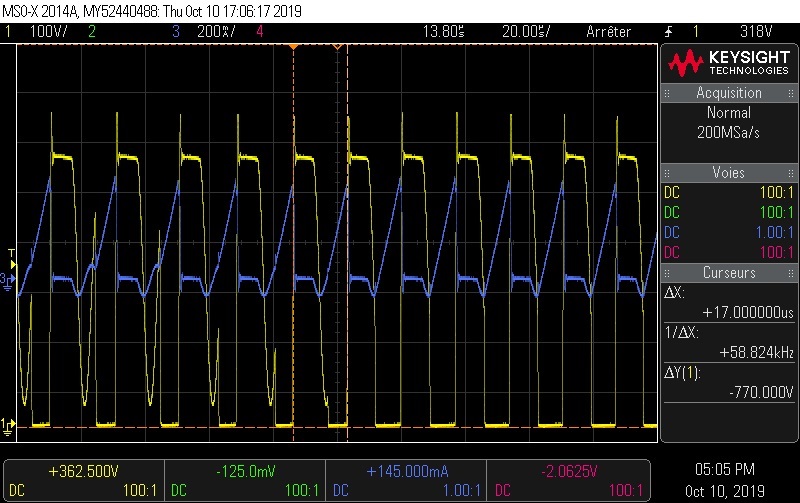

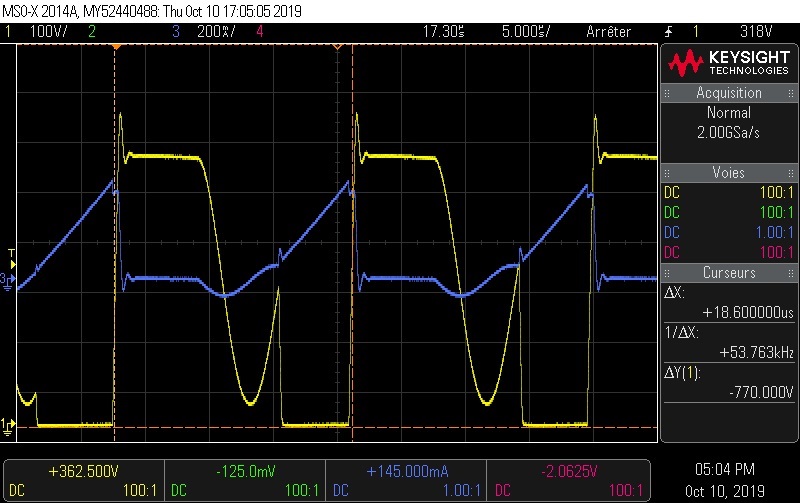

- The mosfet turn-off time. It opens approximatively in 400ns whereas it is given for a turn-off time of 24ns (gate/ source charge = 10nC). So, it is not fast enough to make the zener clamp active. There is only 10Ω on the gate...

- The frequency: our switching frequency is quite low as well, it varies around 60kHz, when we should actually be around 80kHz.

Despite these points, the power supply works quite well, the output voltage is stable (200mV ripple) at the desired load.

How can we gain the missing 20% of efficiency ?

Thanks a lot for your help.

Best Regards.

Nicolas.