The design is almost the same as if you fill in the 30-70V input, 24V 20A output at WEBENCH® Power Designer.

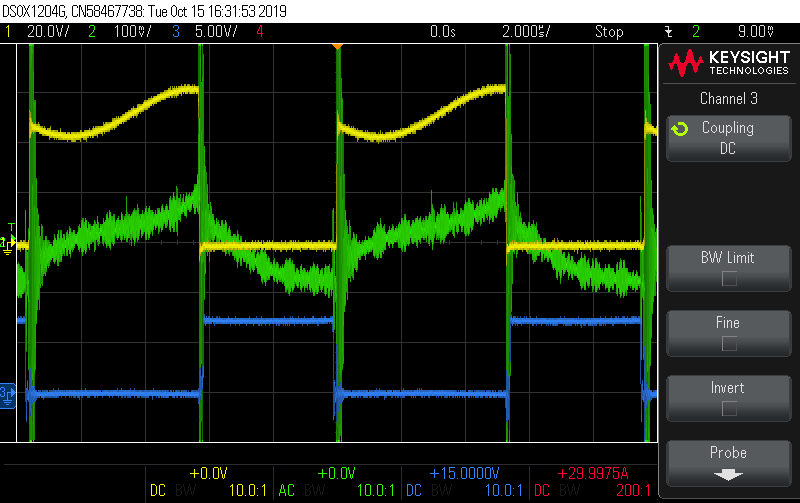

But the actual result is quite far from expected and there are some main problems, output voltage is 24V

1. LM5116 broke down easily, it broke at these situation: 70V input 10A output, broke down immediately; 48V input 13A output, broke down immediately

2. Temperature is quite high, when 60V input 10A output, the temperature rise to 100 degree in 3 minutes.

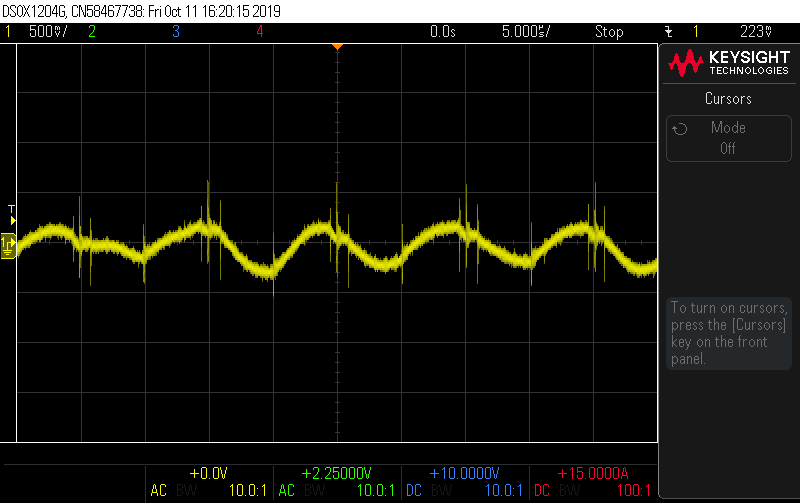

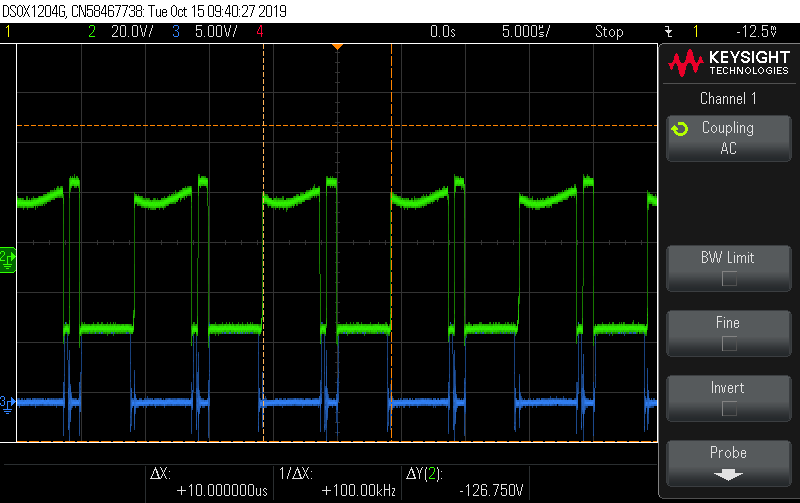

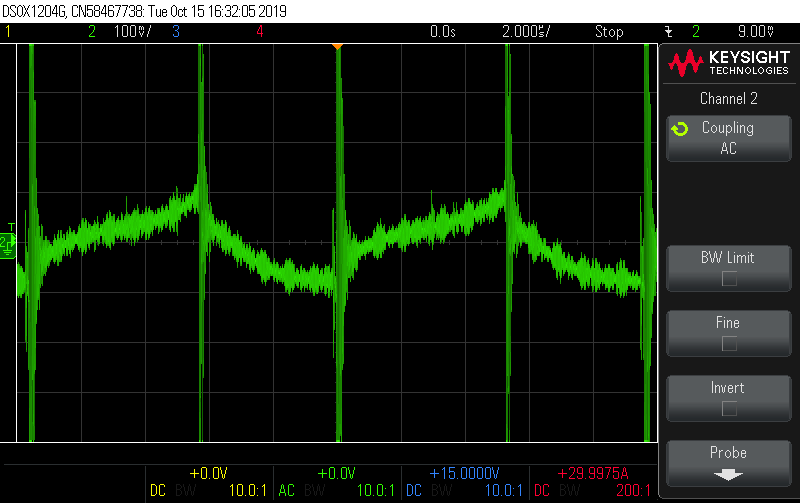

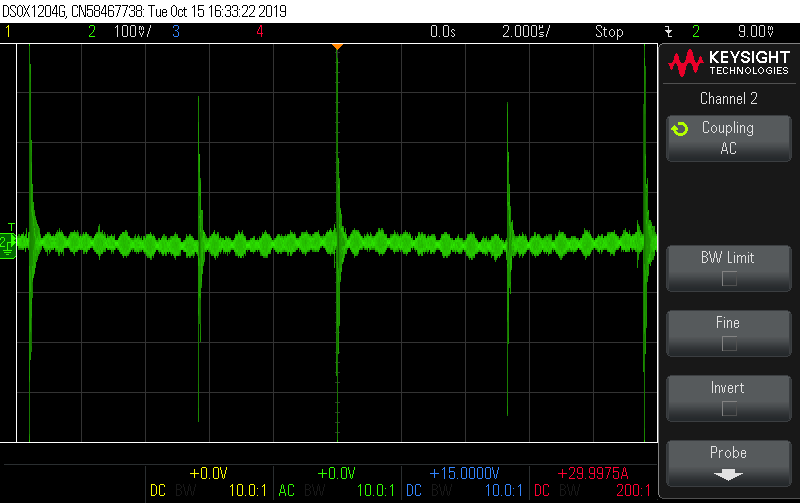

3. Large output ripple, it was about 1Vpp, and voltage spike when MOSFET on and off.

Is there any way to address these issues? Thank a lot!