Hi,TI

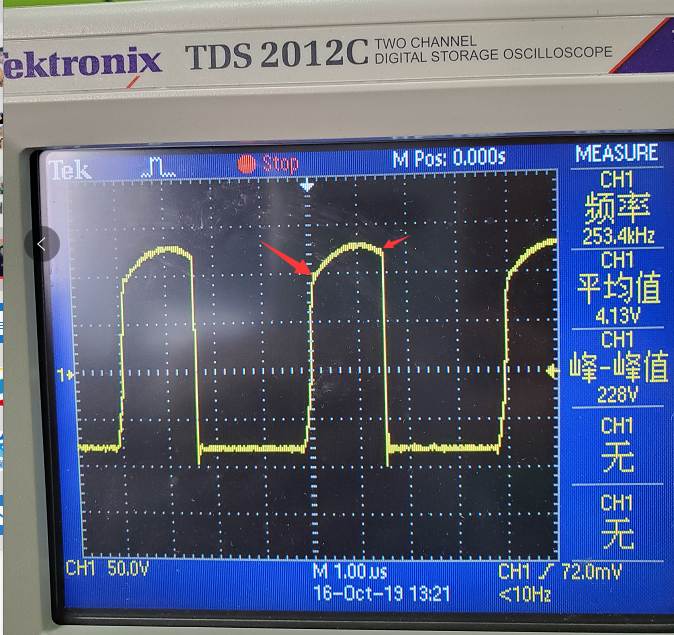

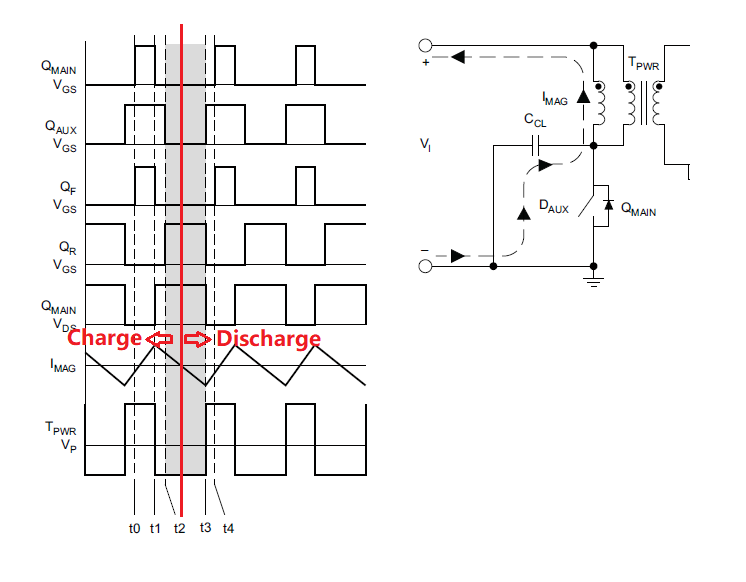

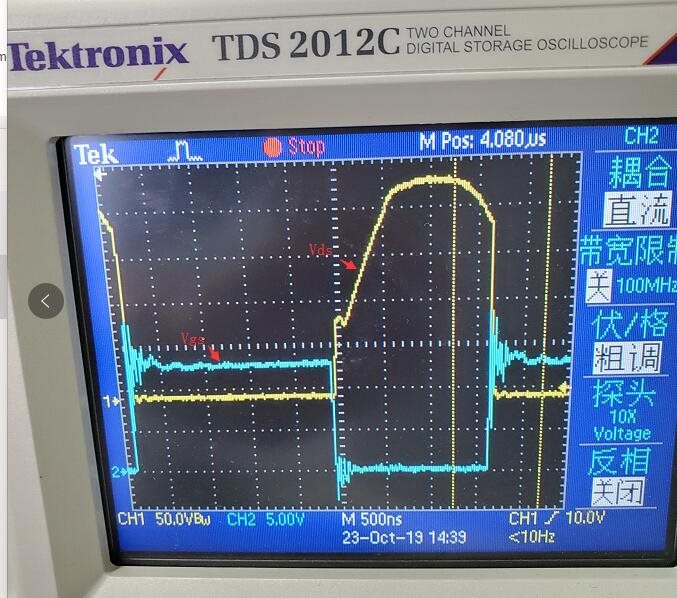

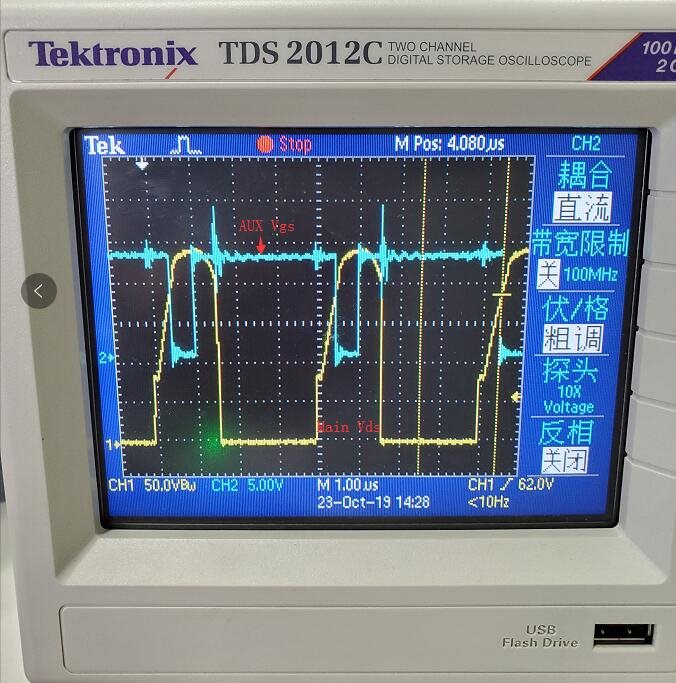

When UCC2897A is used as the active clamping forward power supply, it is found that the Vds waveform of MOS tube is like this. As shown by the red arrow, the charging point of clamping capacitor is inconsistent with the discharging charge. What is the reason?