Hello team,

We have problems with faulty desat trips.

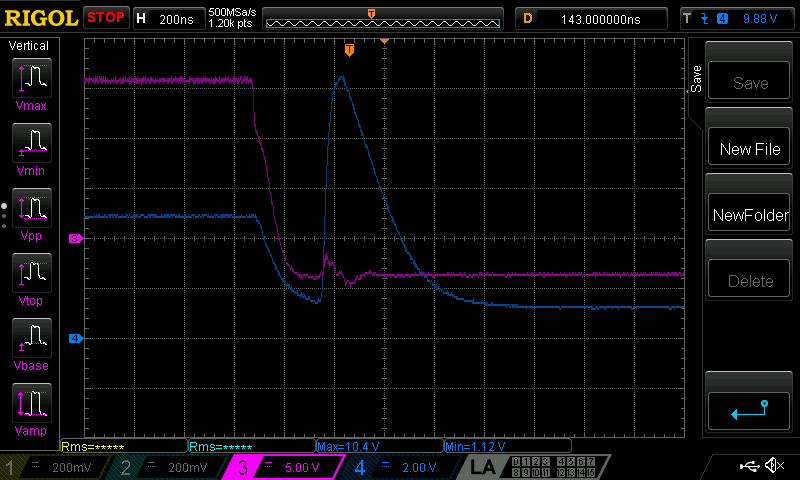

we see standard a pulse on desat (somewhere in our sine modulation) as high as 10V

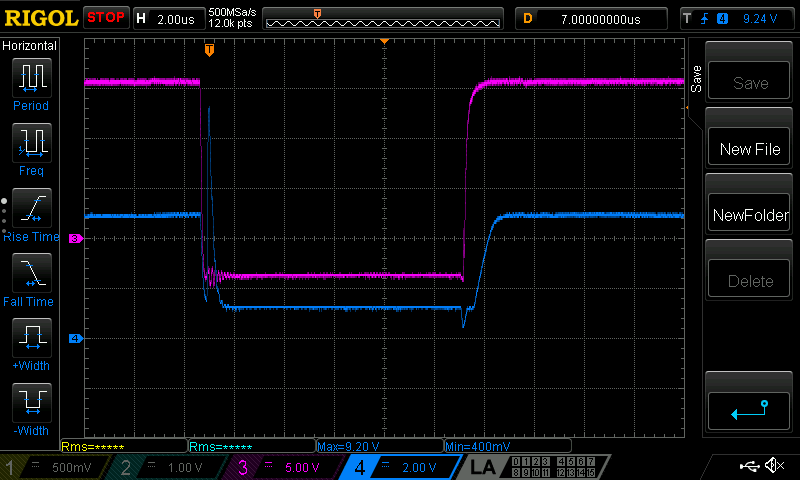

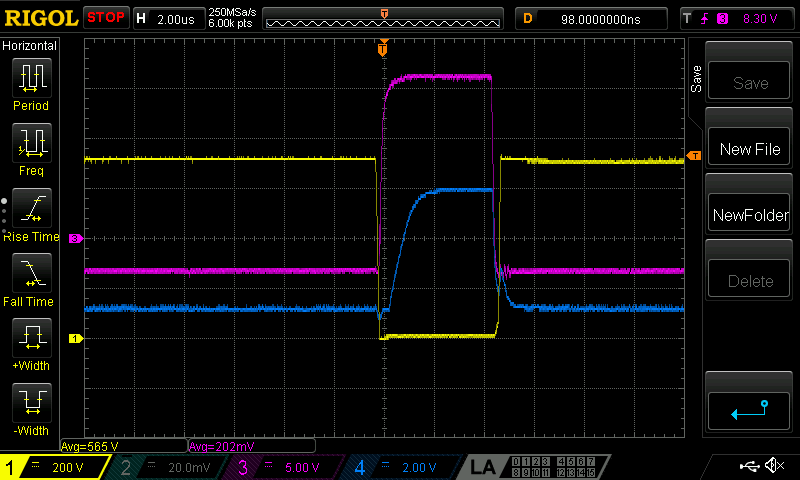

first picture Gate signal with desat pin voltage.

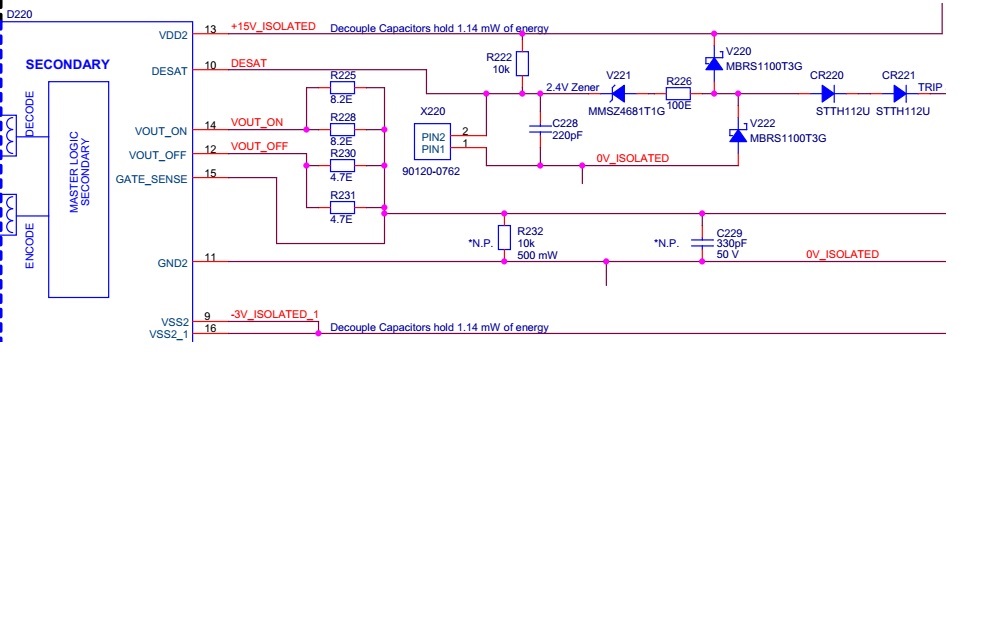

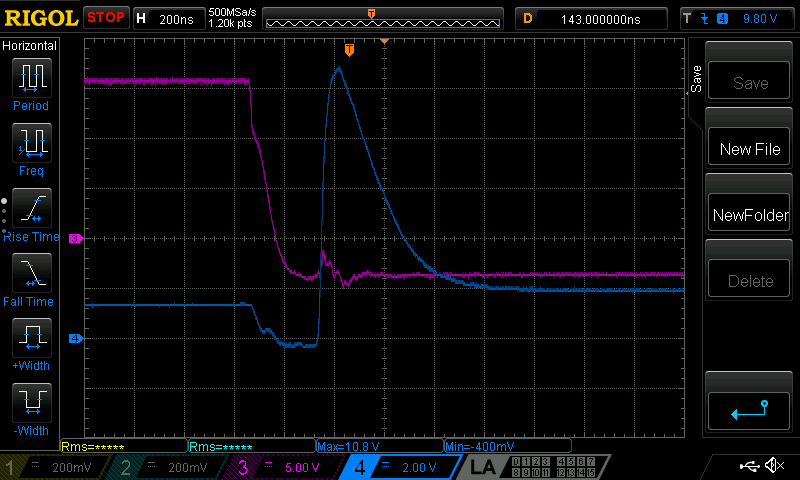

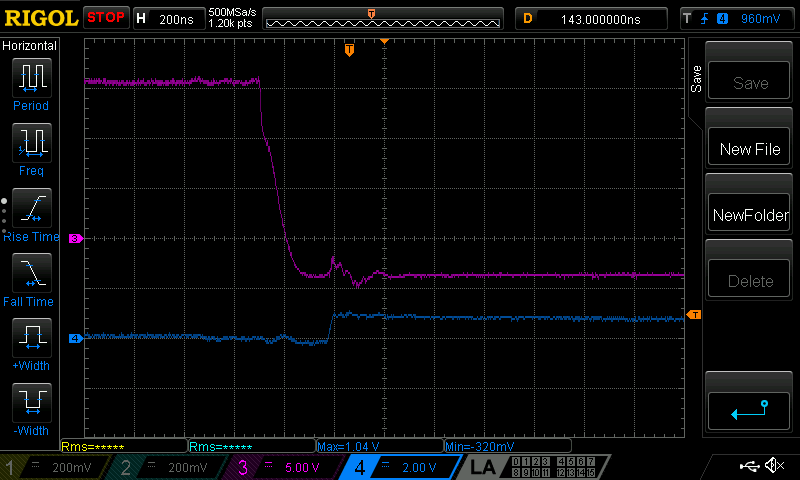

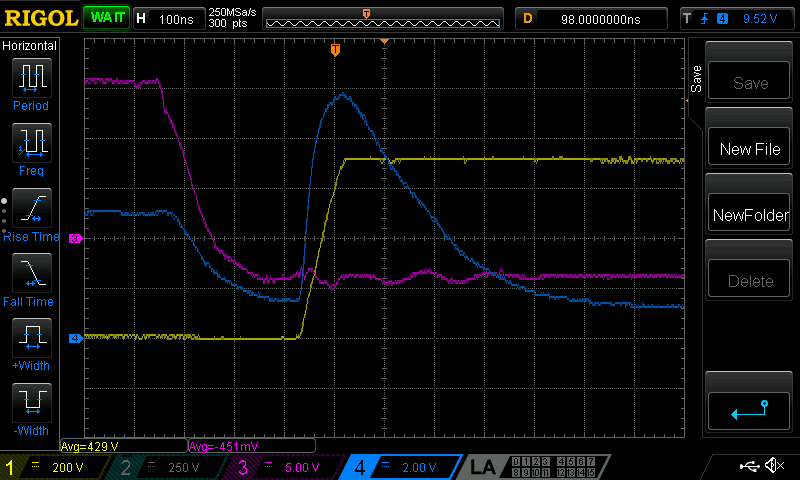

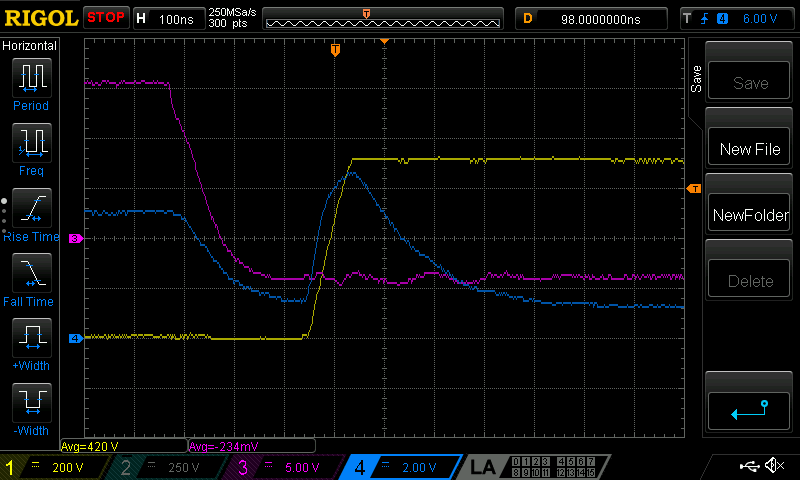

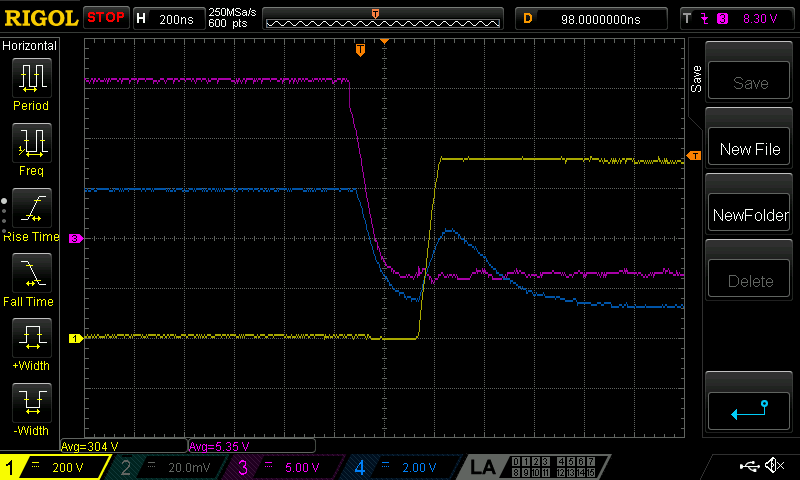

We have two picture with the measurement of the voltage between V221 and R226 first without a jumper on X220 and one with a jumper on X220

It looks like the ISO5852s can't handle the current from the circuitry

P.S. the pin numbering in the schematic are from the ADUM4135 we have replaced it with TI and swap R-ON and R-OFF