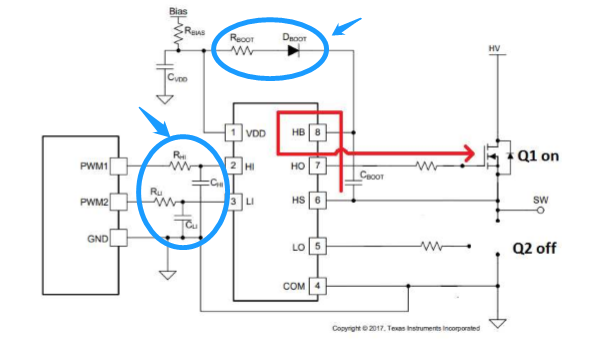

I now use the UCC27211 driver chip to complete the driver task. However, the rising and falling edges of the drive signal reached nearly 100 ns. My bootstrap capacitor and Vcc capacitor are close to the chip pins, and the values are 0.1u and 1u, respectively. I tried to use 1u and 4.7u respectively, but it still has the same effect as before. What should I do? Thank you.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.