Hi there,

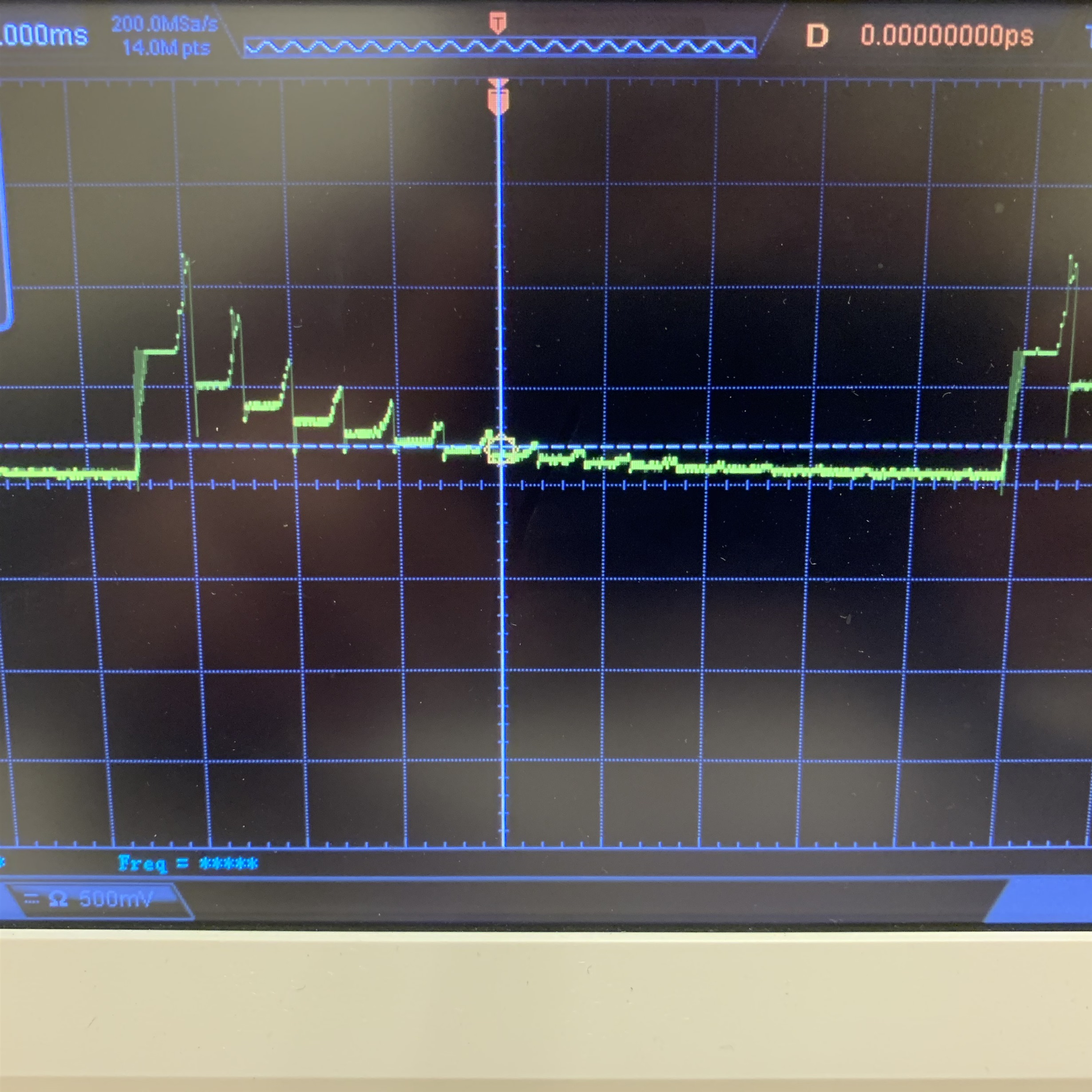

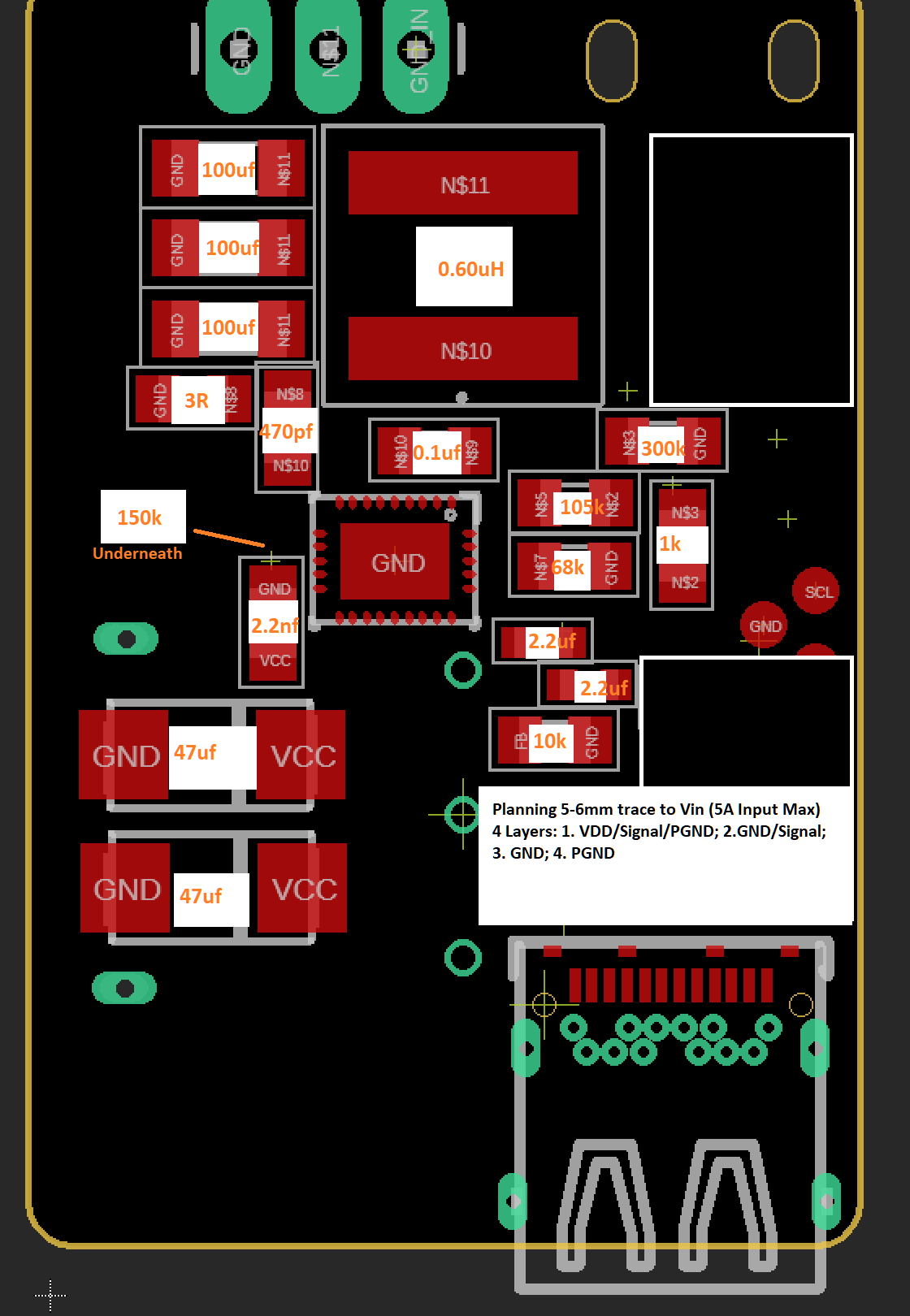

I'm running into some issues with receiving the correct output voltage. I used the Webench tool to design a 1.2-1.8V @13-15A output goal. The source voltage is 20V. I've set the frequency to 300kHz using a 68k resistor. The inductor is 2uH. When I power it up with 19V I received an output of 0.1V and its current consumption is 0.005. I'm certain its properly grounded, it was attached via reflow. I've attached a schematic, board design, and a waveform from the output.

Correction: 28K & 249K for 300khz.