Hi Expert,

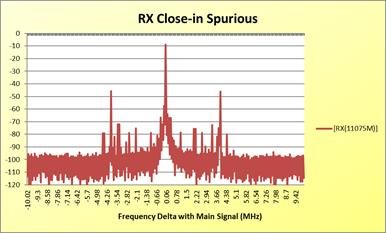

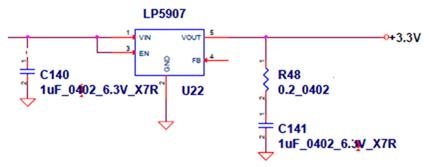

We observe ~35dBc spur at +/-4Mhz offset under -35degC. We tried to touch the chip with hand, the spurs would disappear. In addition, we also found if adding another Cout=4.7uF, the spur would disappear too.

Could you please clarify is it related to the temperature or output cap in terms of stability?

Thanks.

Allan