-

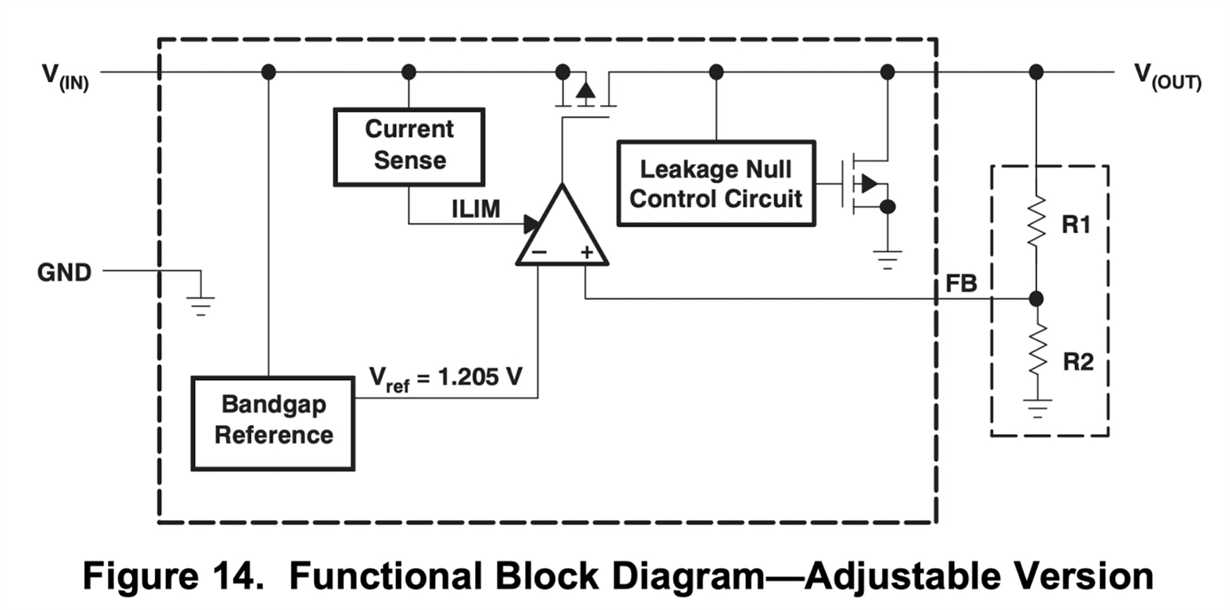

How much current can the low-side FET (leakage null control circuit) sink? Is there a current limit or saturation level?

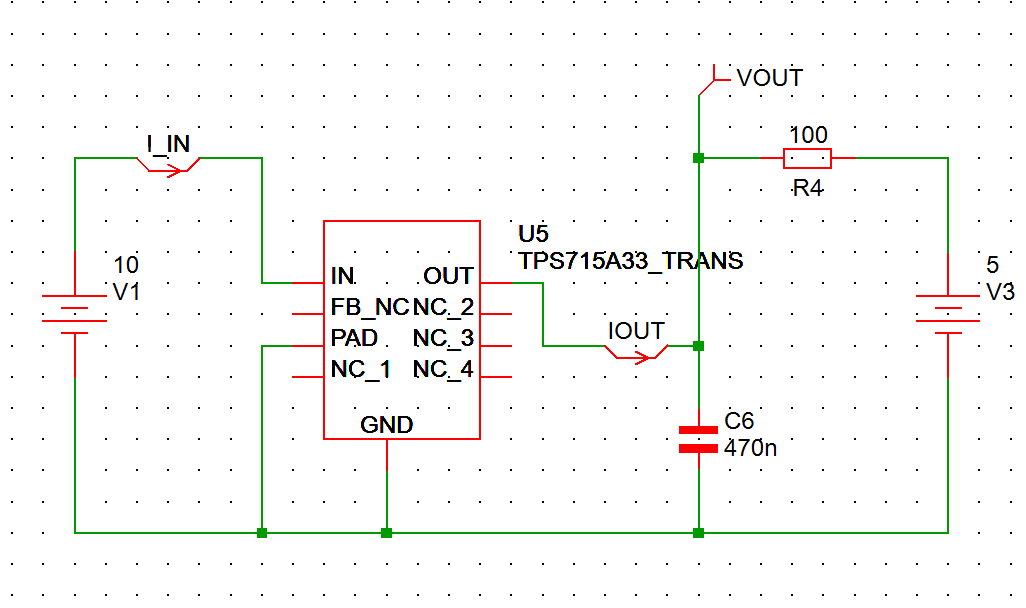

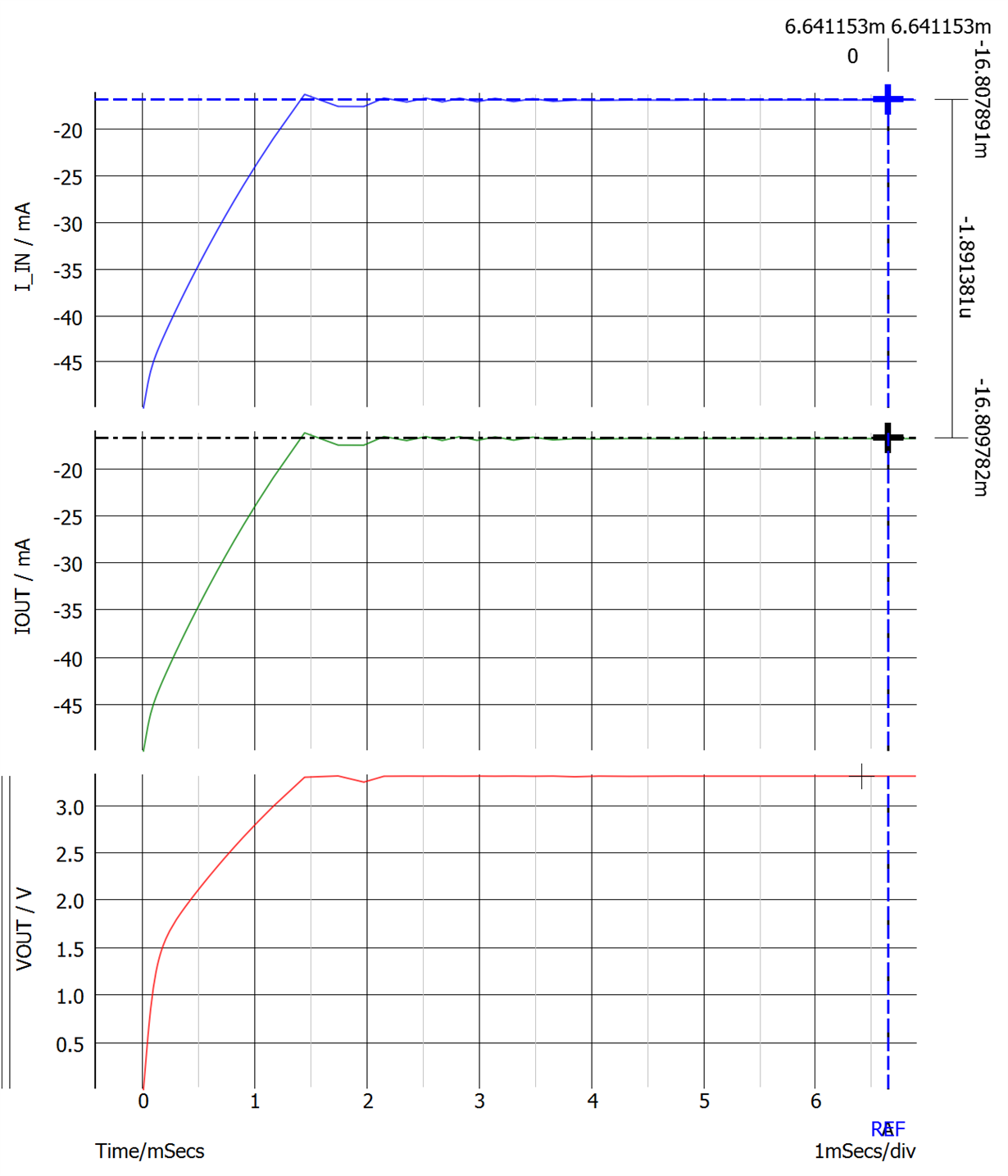

2. Using the unencrypted PSpice model, when VIN > VOUT, and an external source drives current into the VOUT node, the IOUT is negative (current flow into OUT pin), the I_IN is also negative (current flow out of IN pin). Is it the correct behavior? How is it possible?