TO IMPROVE PSRR AND NOISE PERFORMANCE ,which layout is good?

Will the quality of Option 2 be very poor?

thanks a lot

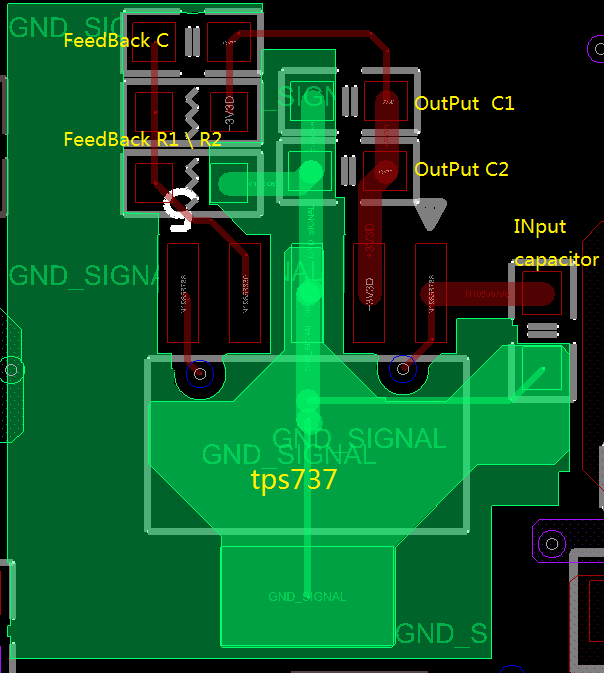

1、Input and output filter capacitors and feedback circuit are placed on the same layer with the IC 373,as shown in the figure below

Put more GND Via under the IC pad。

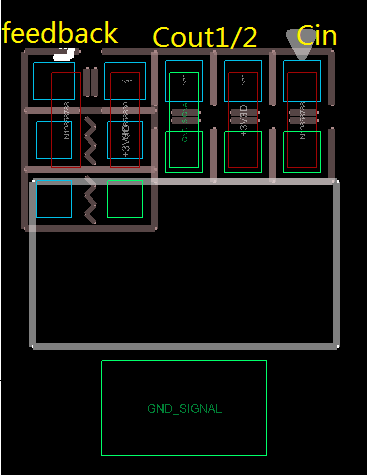

2、In order to save space, the IC TPS737 is placed on the top layer, and the input and output capacitors and feedback circuits are placed on the bottom layer . they are connected through vias.

in the picture bellow ,the red pads are TPS737 which on the top layer , the blue PADS are capacitors which on the bottom layer.