Other Parts Discussed in Thread: LM3488

Tool/software: WEBENCH® Design Tools

Dear Youhao,

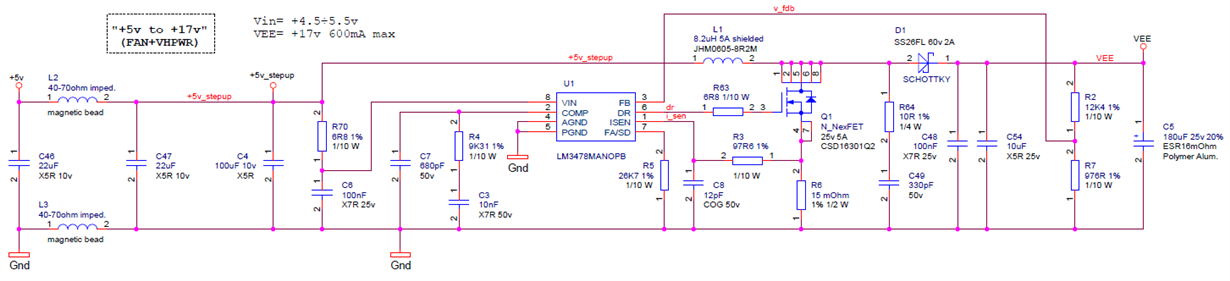

I contacted you 1 month ago to solve glitches/noise/EMC problems related to the LM3478 step-up.

Following the schematic diagram based on your suggestions and based on radiate EMC tests (passed).

NOTE: the R64/C49 snubber filter values have not been tested yet.

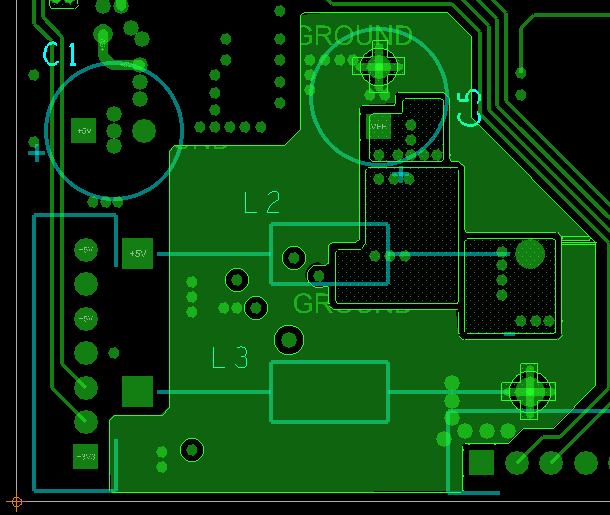

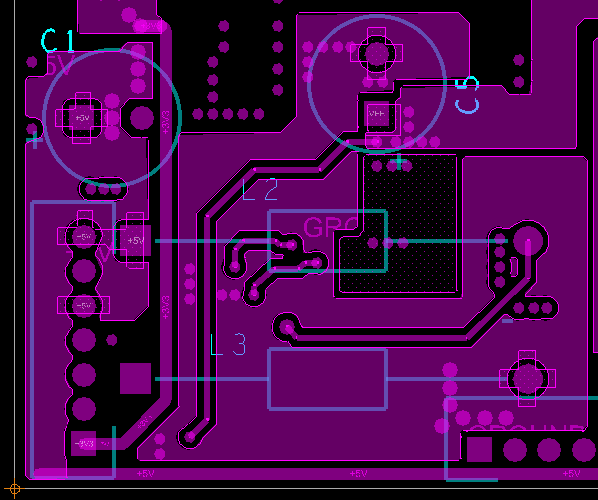

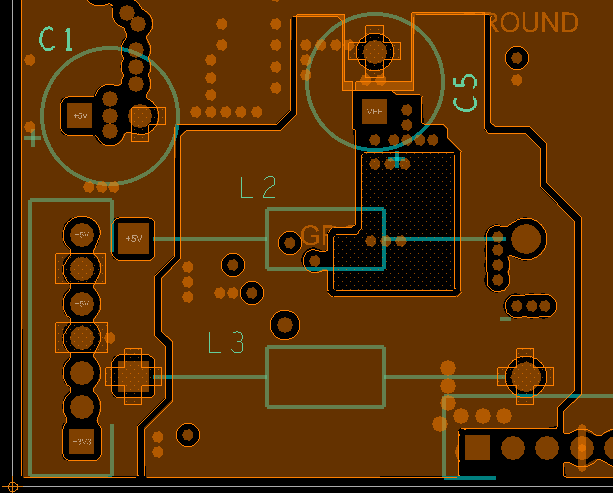

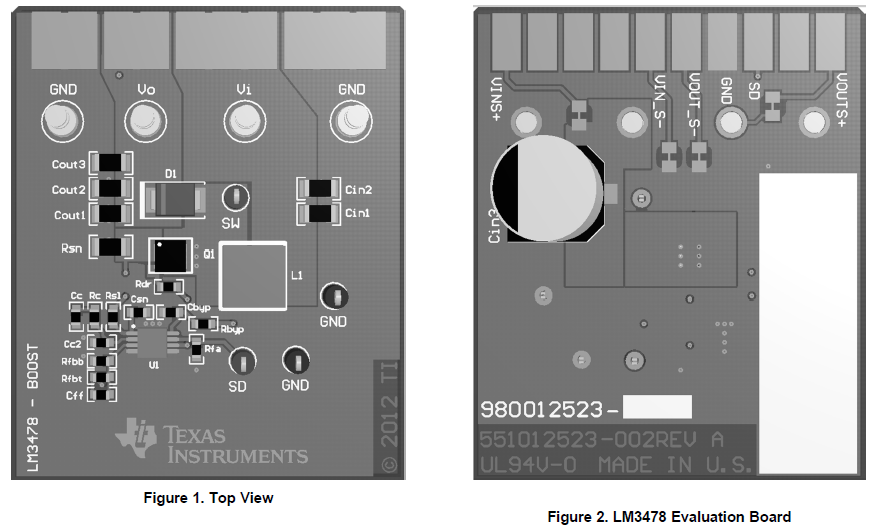

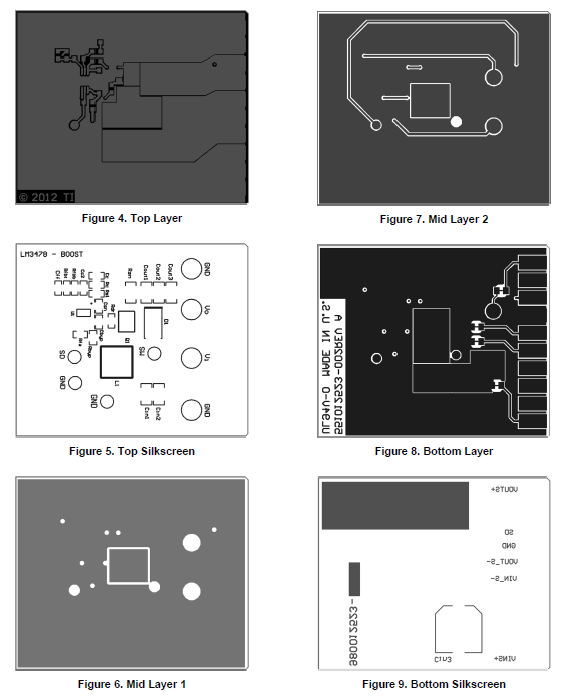

I'm actually drawing the PCB layout (4 layer) based on the attached TI user guide (AN-1204 LM3478/LM3488 Evaluation Board, SNVA656A–June 2012–Revised October 2013)

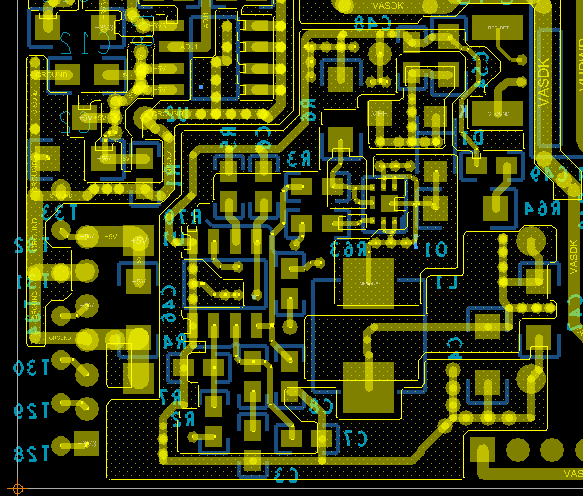

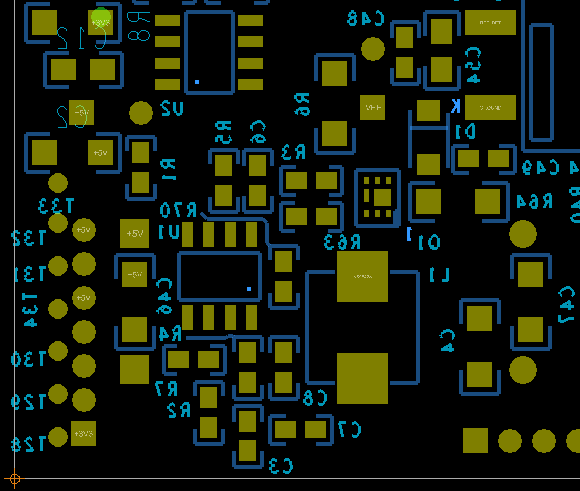

. As suggested inside, I've drawn the PCB tracks wide & short, following same approach showed at pag. 5-6 and 10-11 (GND plane on all the 4 layers).

Below, you could find the PCB layer pictures and component silkscreen.

May you help me about the below question, please?

- in your opinion, the PCB layout approach showed in to the TI user guide is a good method?

- I've drawn a dedicated copper area on all the 4 PCB layers, for the L1 inductor/Q1 nexfet/D1 shottcky net, connecting them together with vias but keeping them separetd from the rest of the planes; do you agree about this approach?

- I've drawn 4 GND dedicated planes (4 layer) connected together through vias in the following points: close to the L3-pin2, close to E-cap C5, close to U1; that planes reach the main GND track of the board circuit, only trough the vias close to E-cap C5; is correct this approach ?

Please let me know if the explanation above is not clear.

Thanks in advance

Alessio