Other Parts Discussed in Thread: LM5112, TINA-TI

hi

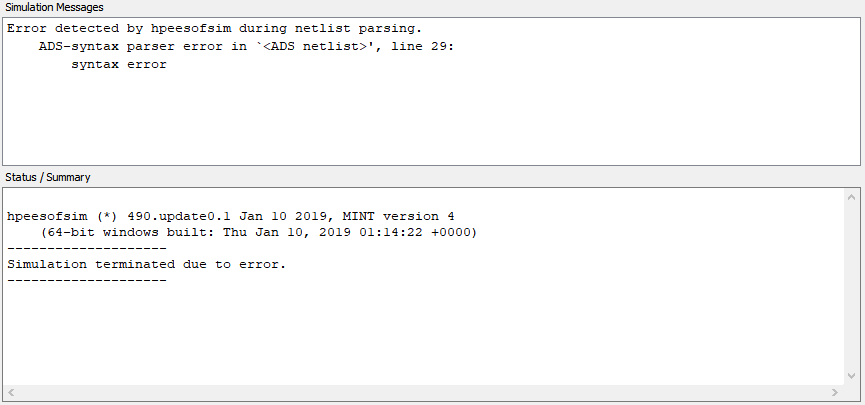

I am trying to use LM5112 spice model in Keysight ADS but it sais it has a syntax error.

I read in one of the threads here that it is due to bad translation off switch models in ADS.

can you provide an updated model for ADS, please