Hi-

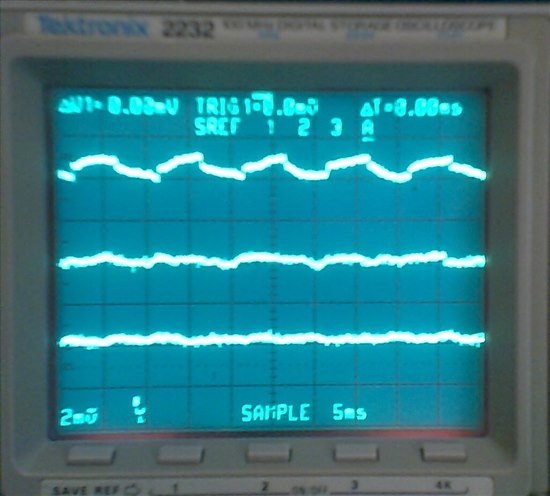

I'm trying to design a system with a 16 bit ADC. While the op amps in the circuit are good, the ADC has little to no power supply rejection. So my understanding is that the power supply needs to be quiet to at least 16 bits. If the input range into the 16 bit ADC is 0 to 5V, each LSB step is 76uV. Thus the noise on the power rail needs to be less than (5 / 65536) = 76uV. I am finding it almost impossible to reach this goal. The noise is comprised of 3 different things. First, semiconductor noise, second noise passing through the LDO from the line side, and third, noise caused by load current variations.

The product is battery powered and I am trying to design this for as low an operating current as possible. I am using ultra low power op amps and they are all using less than a few hundred uA. I am using an ADS8326 ADC. This converter is on only for the duration that it samples and data is read out on the SPI. Then it goes back to low power. It varies between several mA when operating to 0.1uA when powered down.

I have tried LP2992-5.0, LP2985-5.0, LT1761-5, various TPSxxx LDO's and even the new TPS7A4901. All of these parts seem to have really poor load regulation when they are operated with very, very light loads. For example look at the datasheet for the TPS7A4901. Its specification for load regulation is 0.04% of Vout. If it is set for 5V for example, 0.04% of 5V is 2000uV. This, is much worse than 16 bit "quietness". Looking at Figure 17, the curves for load regulation at several temperatures, the problem looks pretty obvious at the very left edge of the graphs. Between about about 5mA of load current and 0, the output voltage varies by a lot more than it does over almost all of the rest of the range from 5mA up to 150mA. So far, the only fix I have found is to put a resistor between the output and ground that draws a continunous load current of somewhere between 5 and 10mA. But this then is not super low power.

Anyone have any thoughts?

Can anyone explain why this is so? I have read through slva072.pdf and don't really see an answer there.

Thanks!

-Randy