hi,

I am facing a issue in emi/emc testing as i have POE based Design using Ic TPS2373-3RGWR with switching IC UCC2897ARGPR as the switching noise is coupling over the Ethernet cable and radiate due to this we are failing in emi/emc testing , due to the switching harmonics at 30Mhz - 1Ghz range the complete noise floor increased and fails, we have tried a couple of options but it never reduced but at last we tune the common mode choke then it shows some effect but not much.

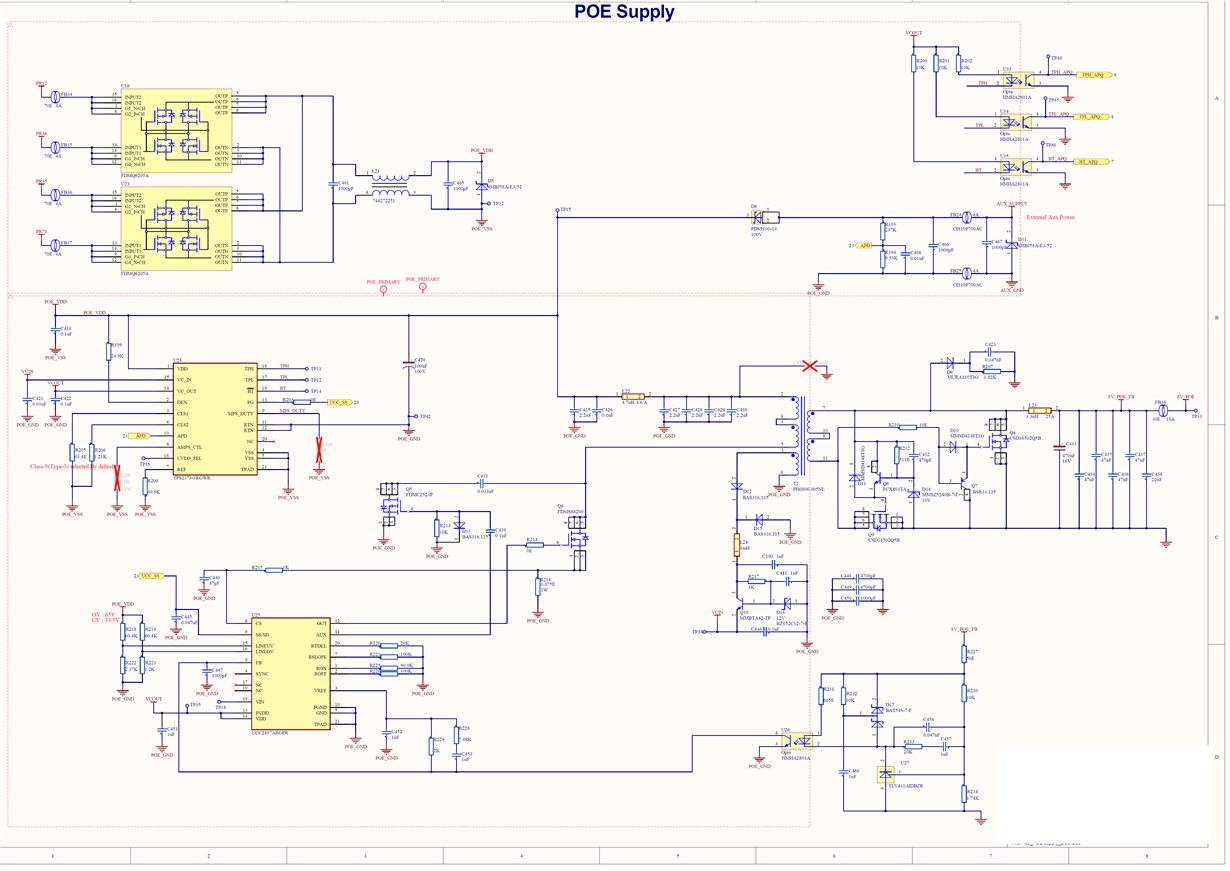

I am attaching my schematic for the reference, please suggest the options so that we can pass the emi/emc prescan testing.

In this 1st one is with near feild probe and 3rd one is anechoic chamber result.

Regards,

Pankaj