Other Parts Discussed in Thread: UCD3138,

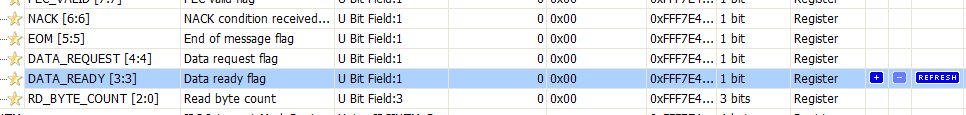

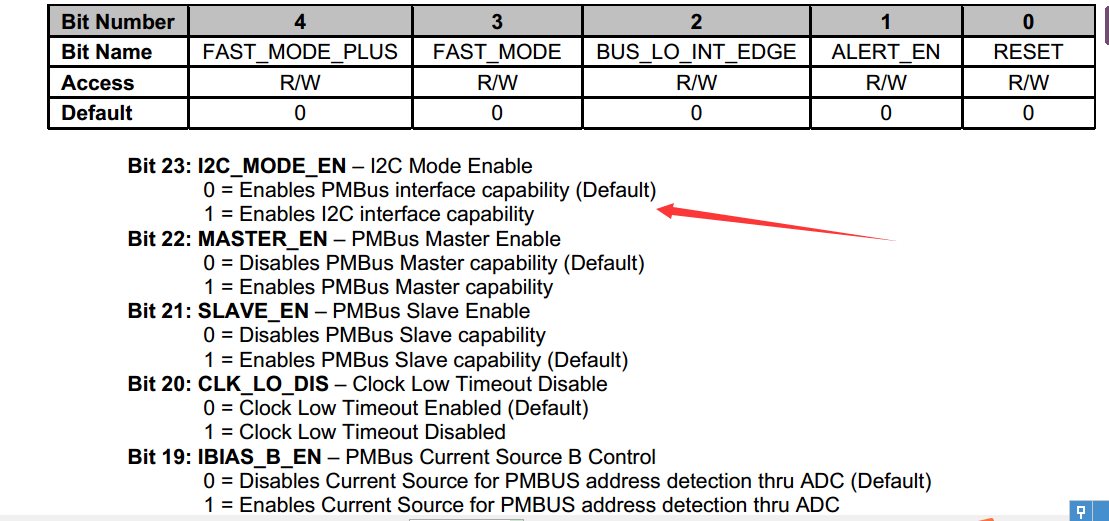

During debugging IIC communication, it is found that after receiving the data, Register DATA_READY is not set, and Register RD_BYTE_COUNT is also always 0.I want to know what is the condition that DATA_READY register was set 1.

I want to process the data according to the location of the DATA_READY flag. What should I do?

Thank you very much!