Hello,

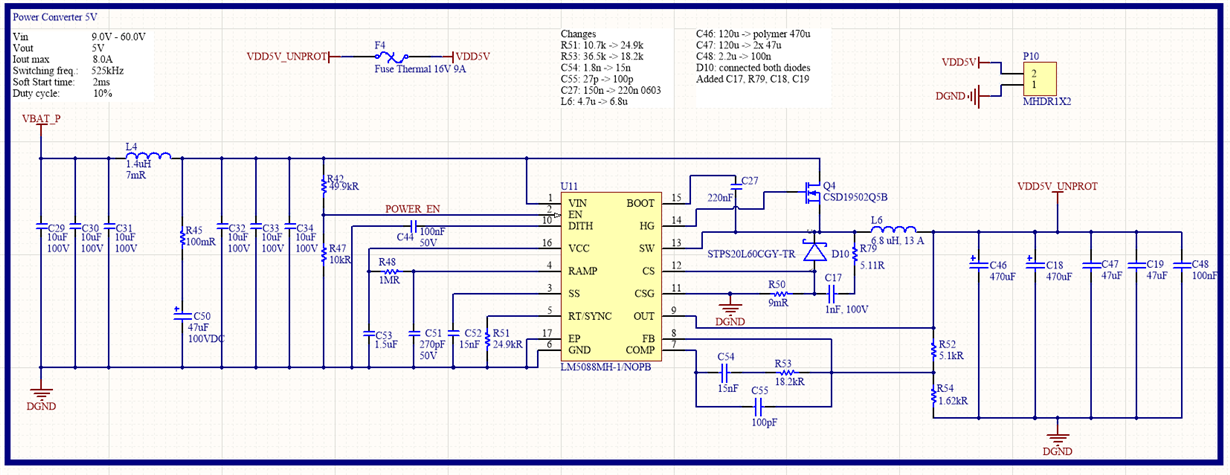

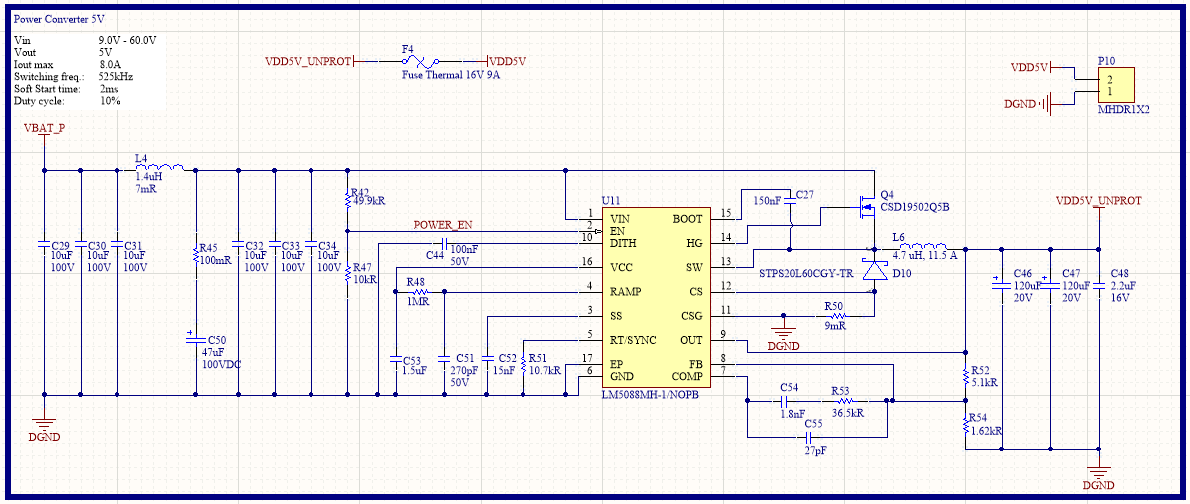

For a project I am developing a DC/DC converter with the LM5088. Vin(min) = 9V, Vin(max)=60V, Vout=5V, Iout=8A. I made the design based upon the design that Webench provided me with.

Below, a picture of the schematic can be seen.

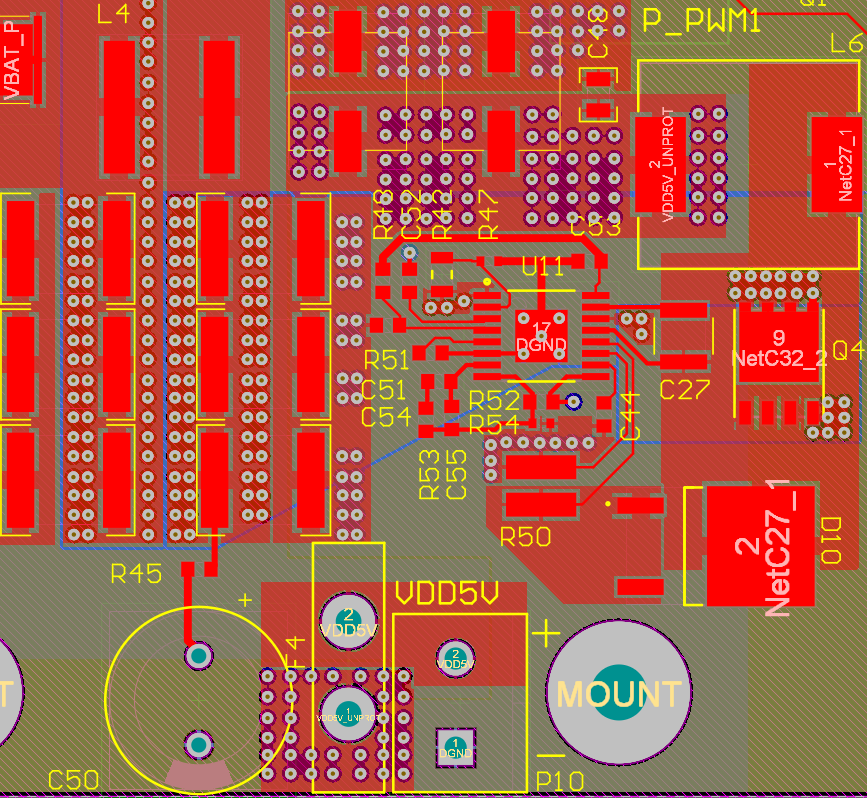

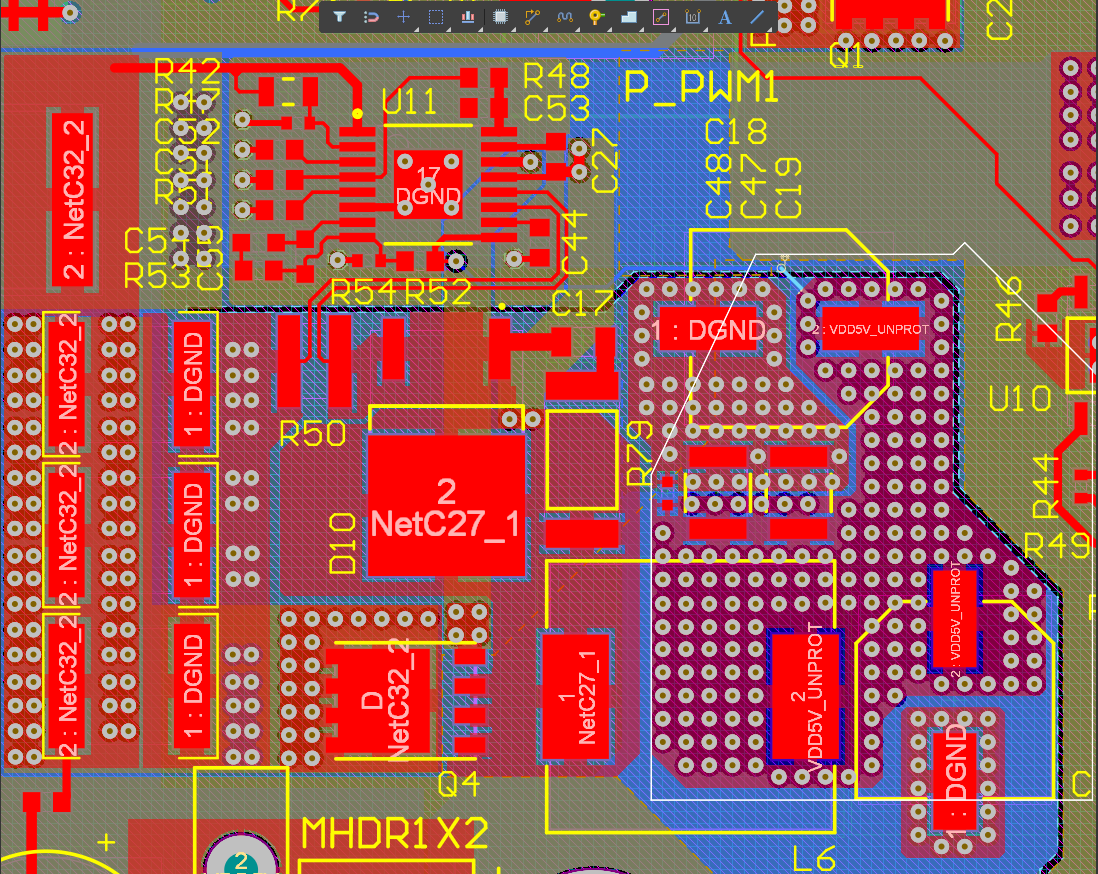

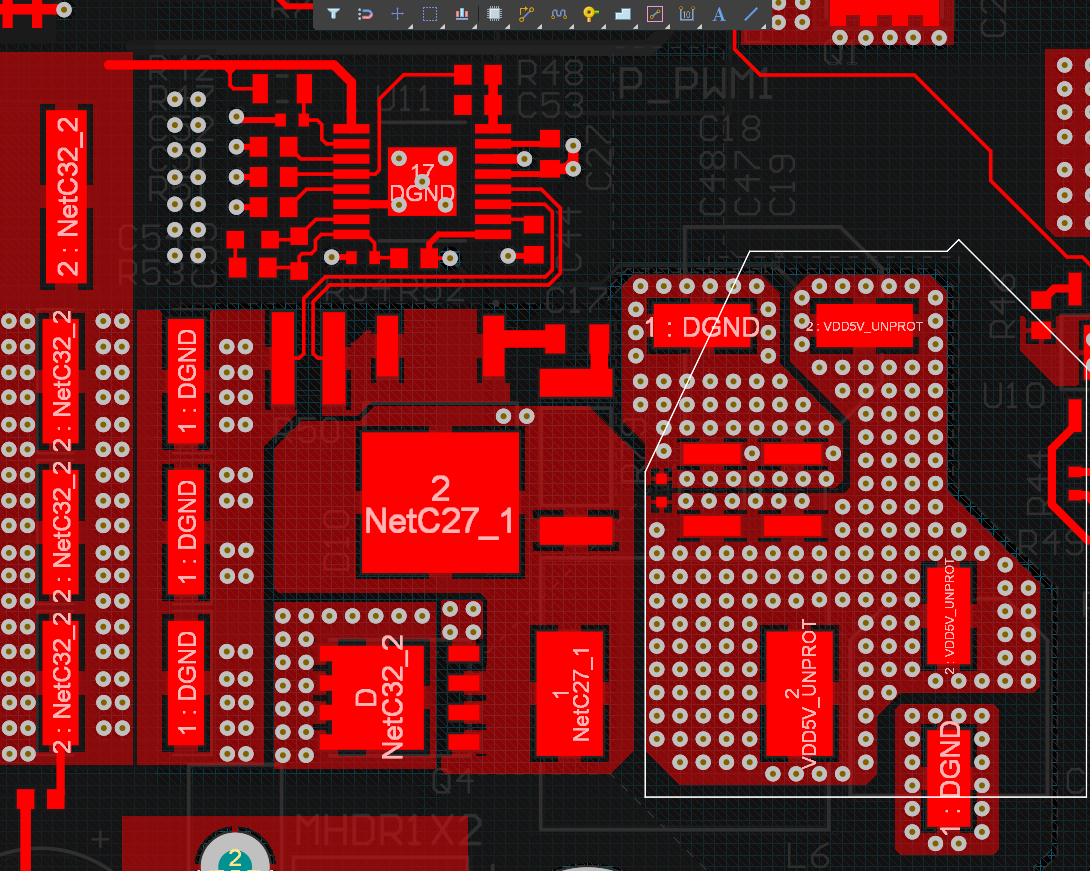

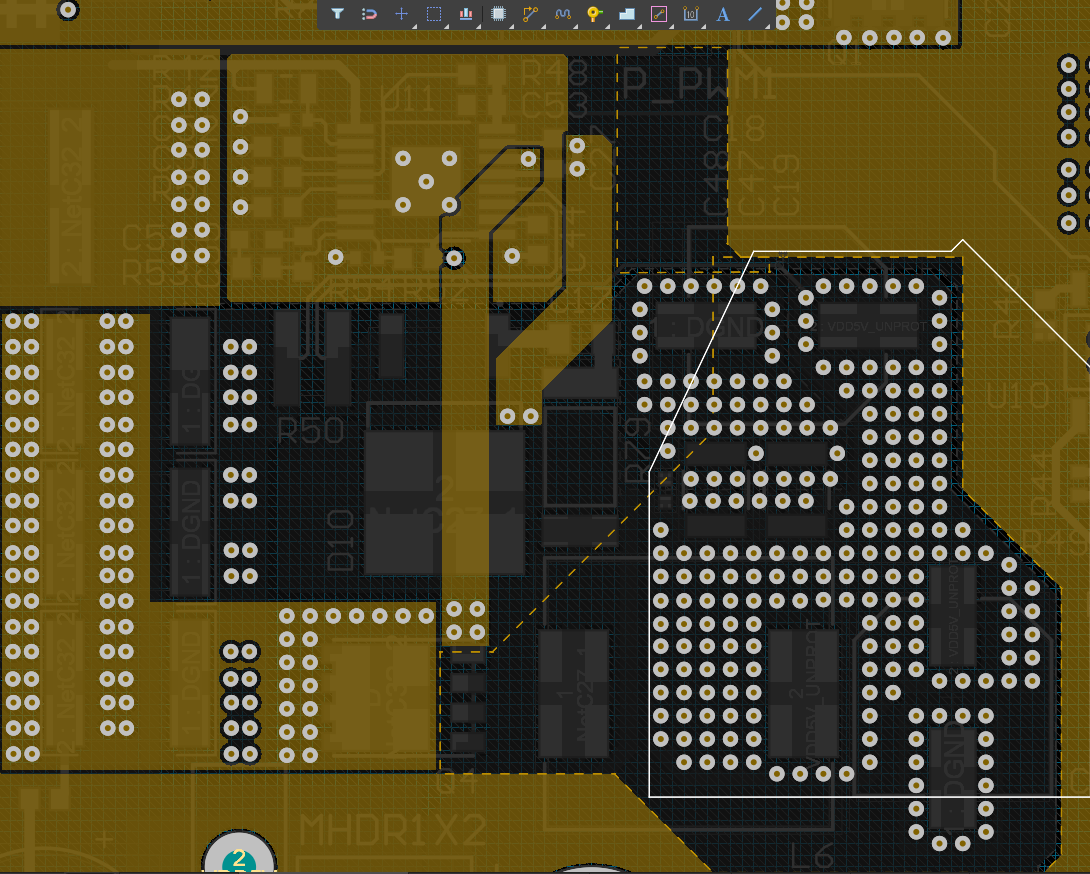

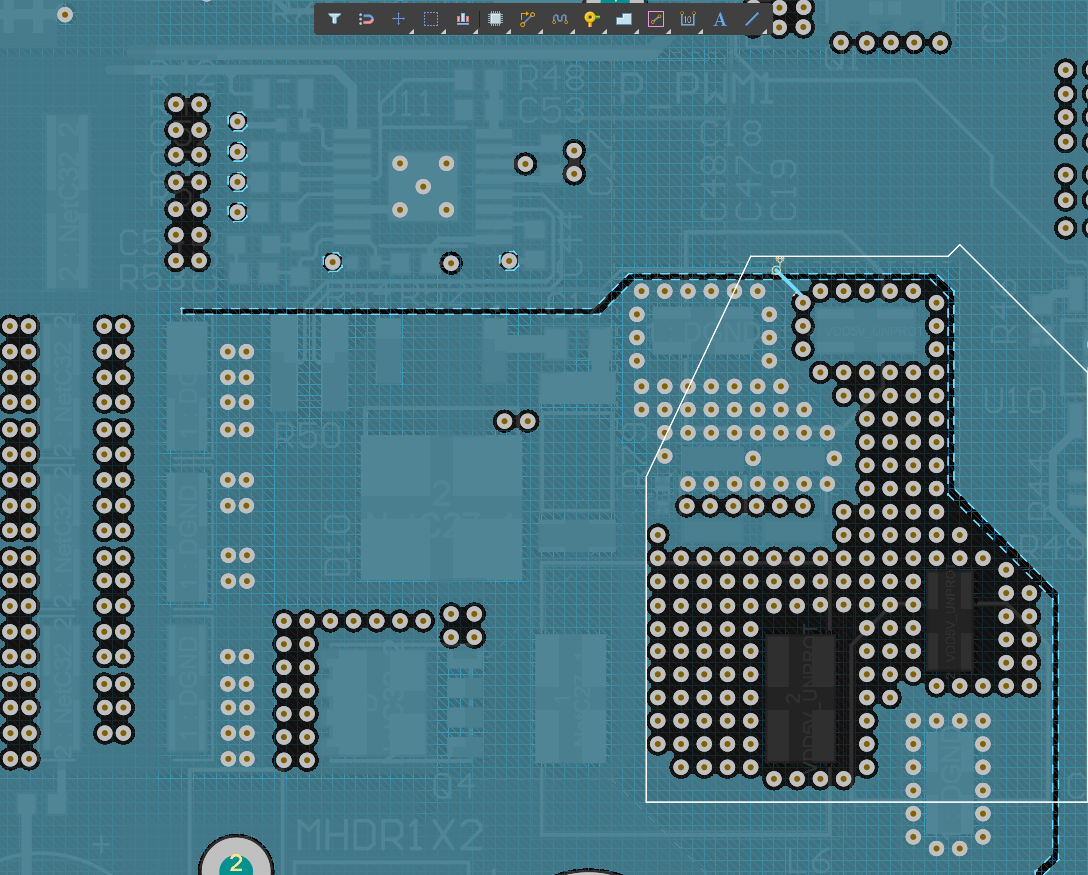

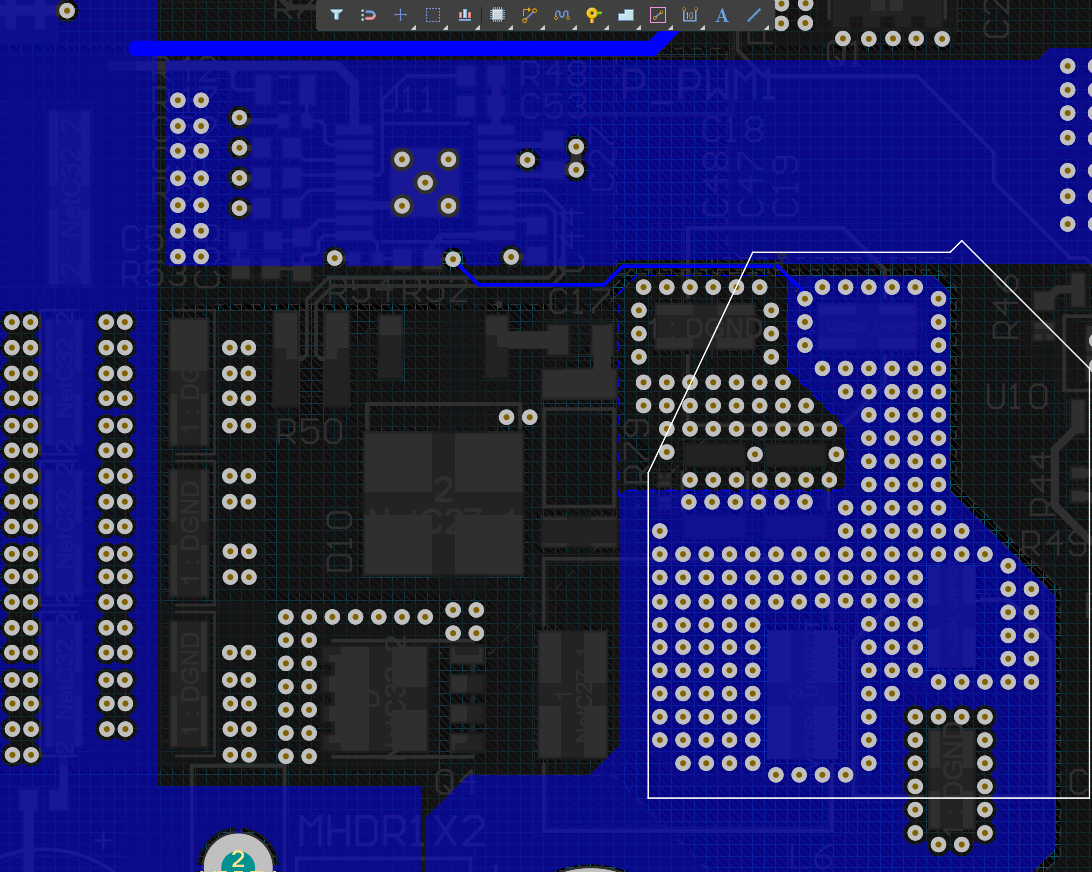

Also the PCB layout is provided below. I can provide you with entire PCB layout in mail if that helps.

I have the problem that the 5V output is not stable at high Vin(>20V) at high load (1R). When input voltage under or 16V, everything is fine and the output is stable 5V. However, when Vin increases from 16V to 20V the ripple gets worse, the converter starts making a high pitch noise and the dithering stops. The 5V output decreases and then drops to >3V.

At a load of >50R, all is fine. At every voltage from 9V to 60V the output is stable 5V.

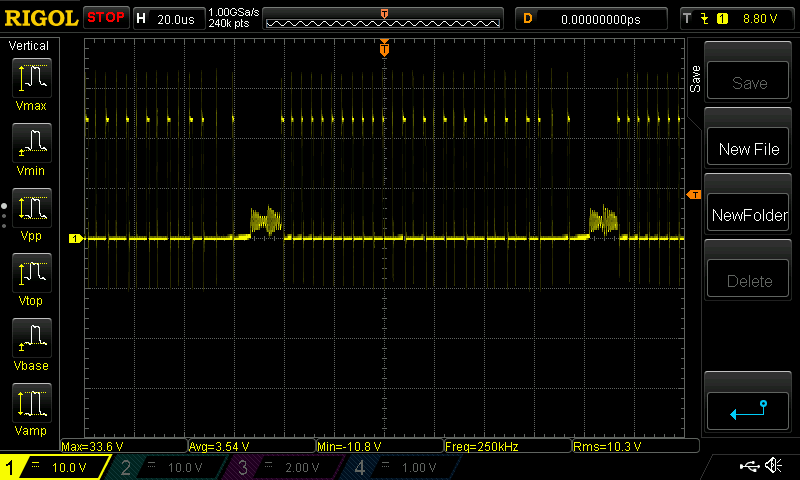

The screenshot of the scope below shows the Source voltage during operation at 16V input voltage with 50R load.

As you can see, the switching is neat and constant. Also, dithering is present. This can be seen at the scope where the frequency changes but can obviously not be seen in the picture of the scope.

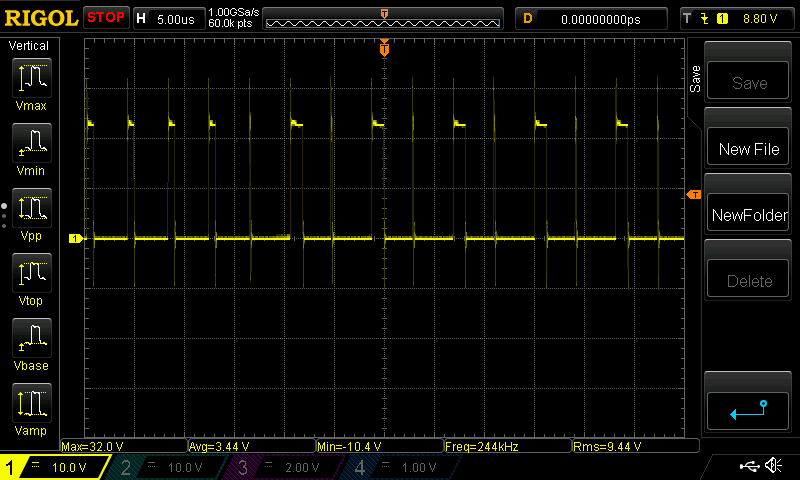

The screenshot below shows operation at 24V input at 1R load.

As you can see, the converter does not operate properly. Below, a zoomed in screenshot can be seen.

It can be seen that the switching pulses are not constant. Sometimes, a very short pulse is made. After multiple of these very short pulses, the converter shuts down for a certain period of time, as can be seen in the screenshot above.

I already tried to change compensation network to exactly what is placed on the LM5088 Evaluation Board but this did not help. Also I changed the output capacitors bigger/smaller and more/less electrolytic/MLCC to create less ESR but no success. Current sense resistor was made smaller (5mR) and bigger (10mR) to see if that made a difference. It did not make a difference and at high input voltages (>20V) the output is not stable 5V and drops to >3V (with heavy ripple)

I asked few different people with knowledge but none of them were able to find the problem. I hope very much that you are able to help me, as this is holding the project back a lot since I cannot conduct further tests with the PCBA. I would like to hear from you.

Thanks in advance!