Other Parts Discussed in Thread: UCC28C45

Tool/software: WEBENCH® Design Tools

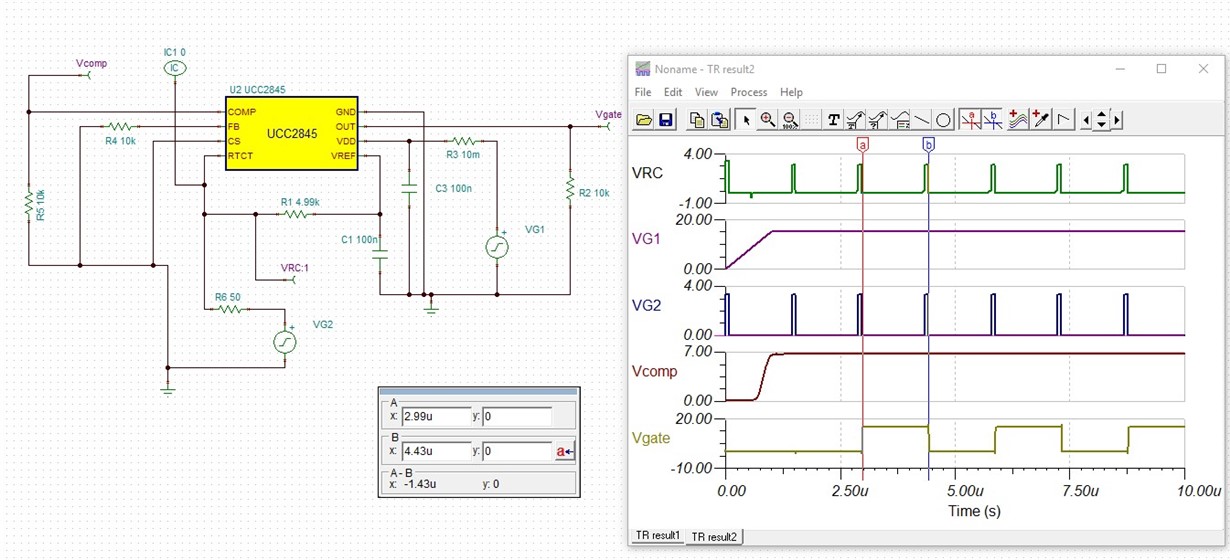

We are seeing a discrepancy in the PSPICE unencrypted model that does not agree with bench results. We have verified the UCC28C45 model has the same behavior.

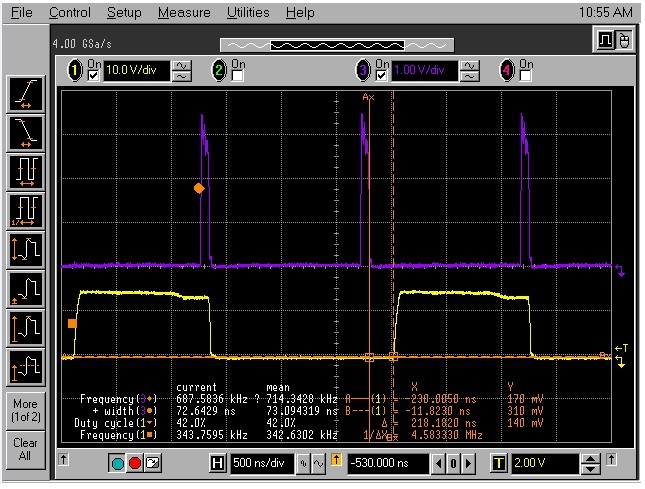

The output duty cycle achieved in the spice model is nearly 50% given a sync pulse of ~70nsec and an oscillator frequency of ~ 684kHz. Actual measurements show a delay from the falling edge of the RTCT input pulse to the rising edge of the output of ~ 220nsec. This limits the achievable duty cycle. It appears this delay is not being properly modeled - please confirm.

Compare this to the measured signals :

Channel 1 is the output, Channel 3 is the RTCT input

COMP, FB, CS are all tied low with 10kohms. Vcc is 15V.

If you confirm this, can we update the models to include the delay to match the actual performance?

Thanks!

Steve