Other Parts Discussed in Thread: LMG1210

We are using the LMG1205 as a driver for a GaN Halfbridge made of EPC2001C FETs.

Lately we had some issues with FETs burning under certain conditions (switching high currents).

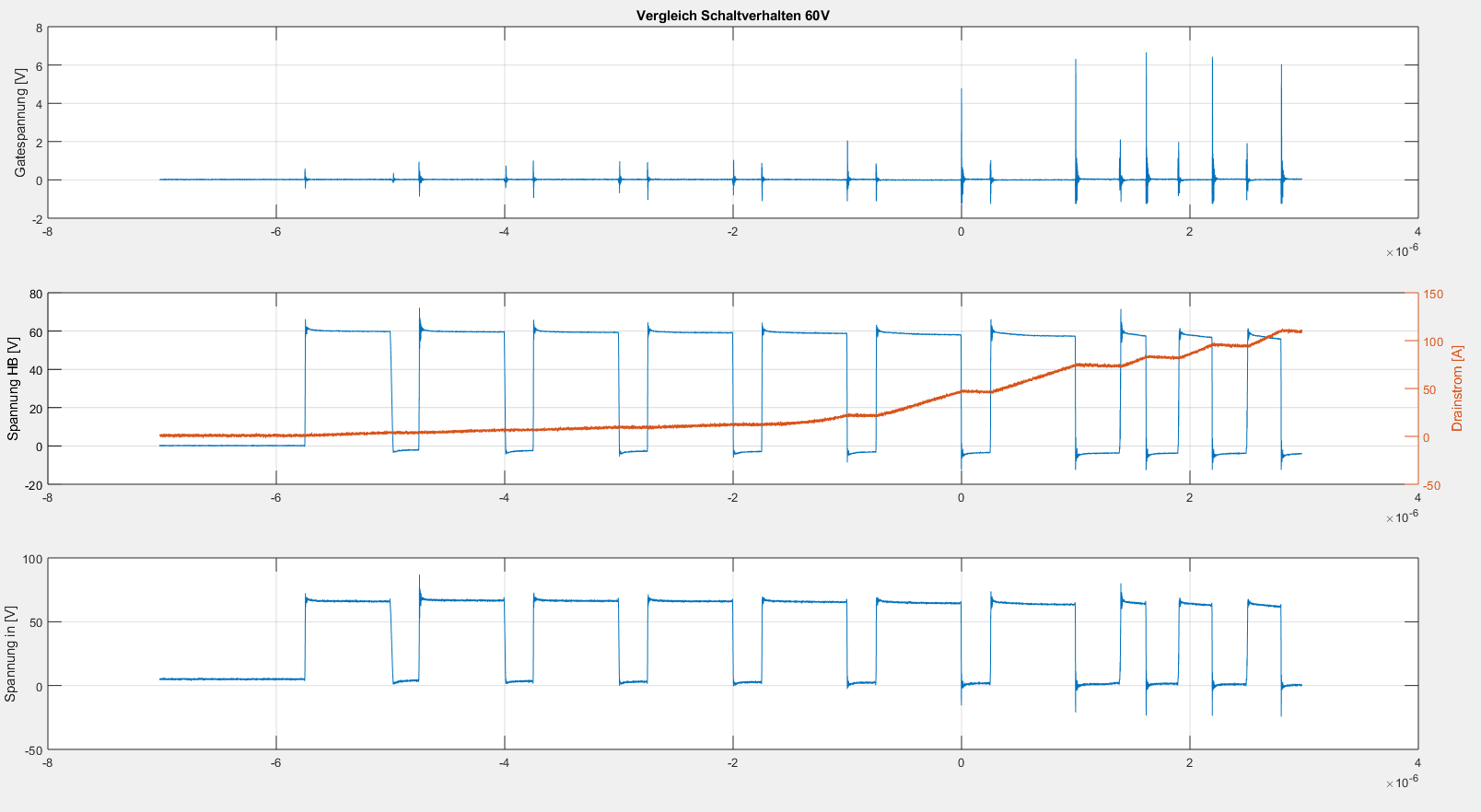

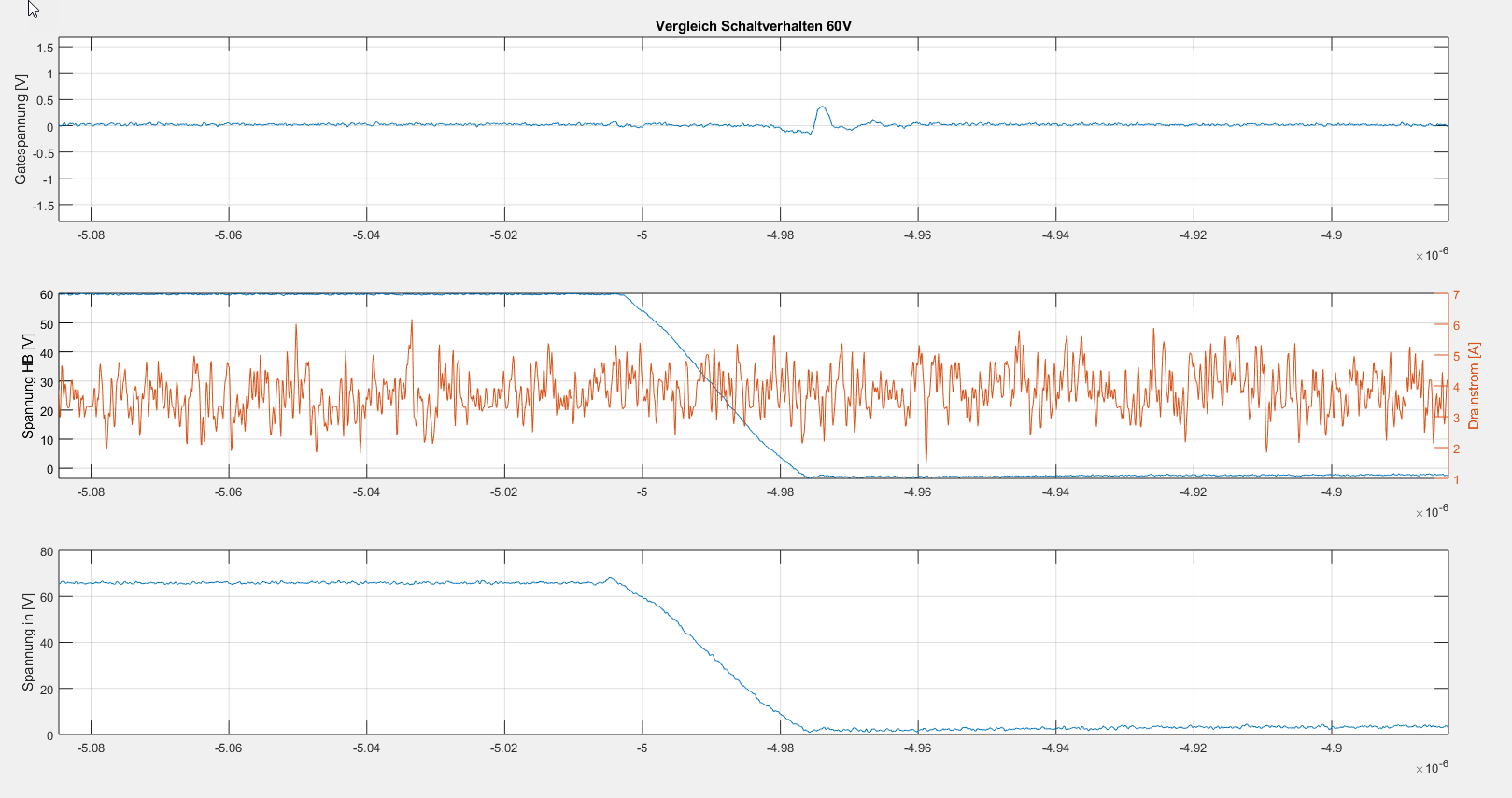

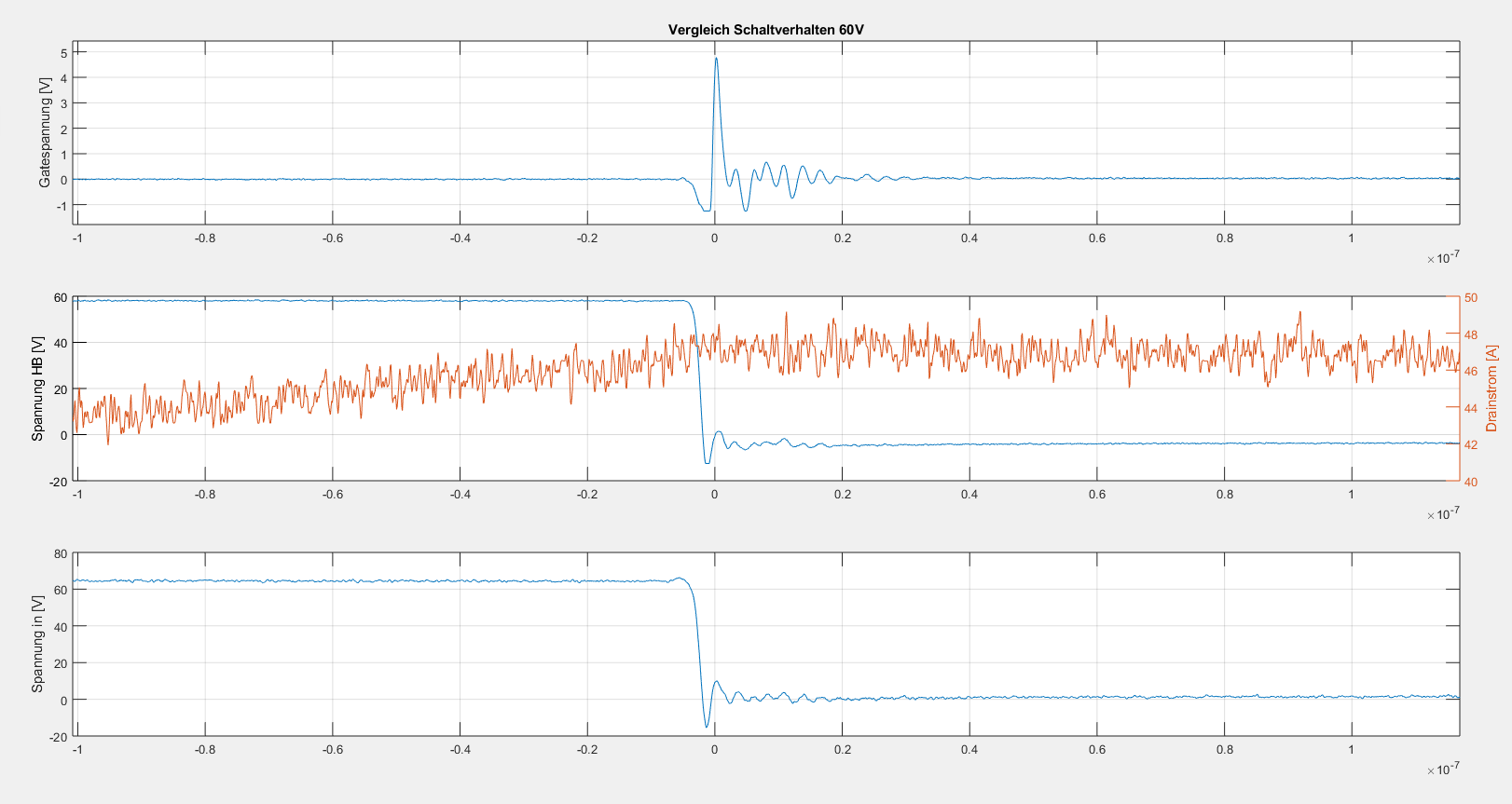

To find out the cause of this behaviour we performed a double-pulse test. We saw an oscillation on the gate signals dependent on the current we switched.

In our view the problem is caused by a high dU/dt (gets even higher the higher the current is) which causes a current across miller capacity and causes an impact on the gate voltage.

But we are a bit concerned about the overshoot which follows afterwards (causes cross-conduction). It is an oscillation with about 300MHz.

But now to my question:

I know, the exact behaviour is an interaction of FET, driver and PCB. But our guess is that the oscillation is caused by a resonance of the driver output (maybe the bodydiode of the output stage?).

Do you have any data about the transition behavoiour of the outputs? Are there any resonance frequencies?