Other Parts Discussed in Thread: TPS7A83A, TPS7A90, UA78

Device: uA78M05IDCYR

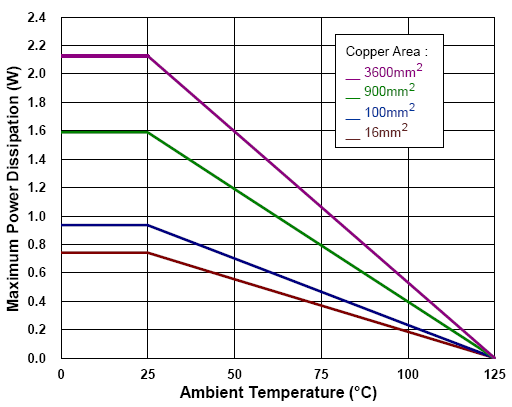

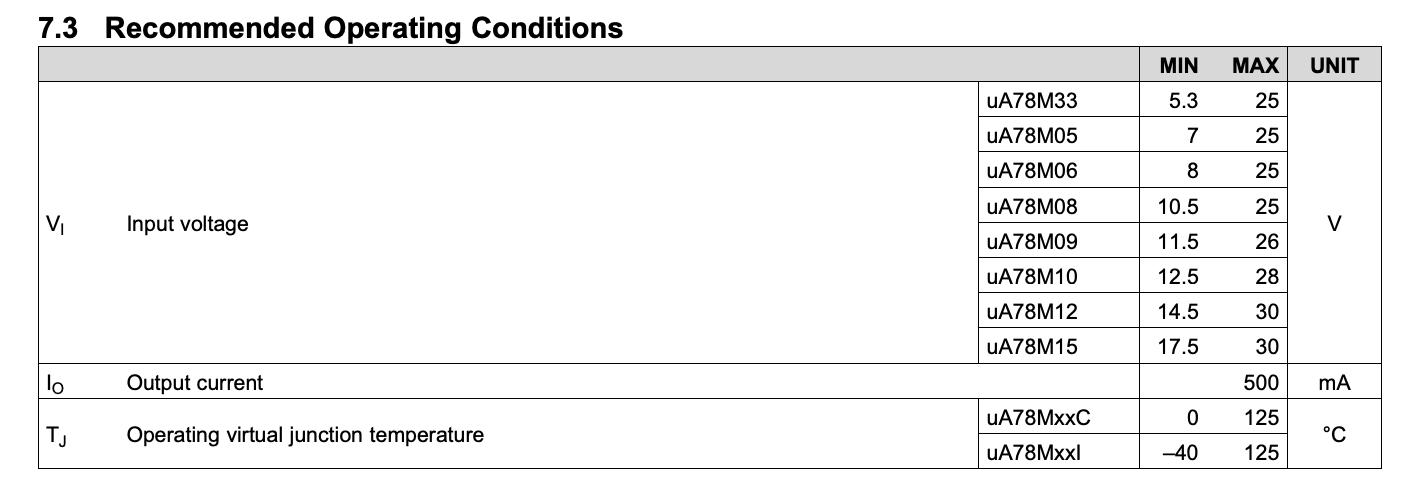

Vin: 22V

Vout: 5V

Iout:50mA

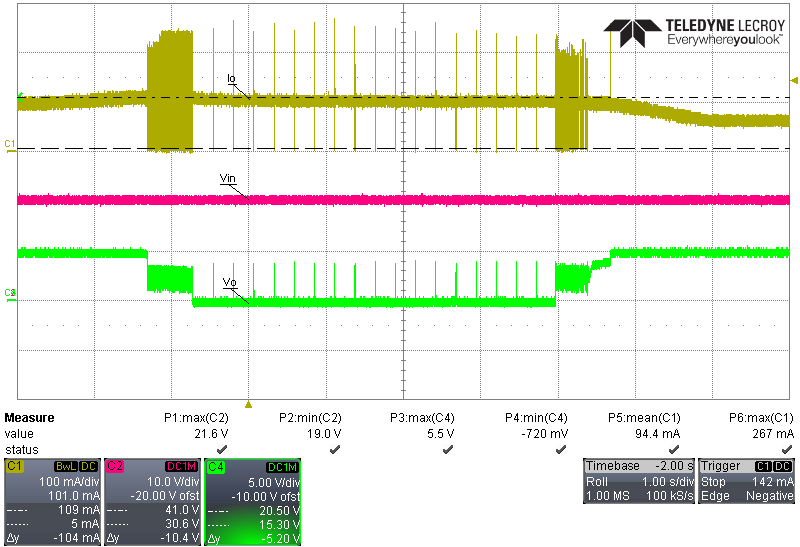

Problem Description: When Input voltage is up to 22V with 50mA(ambient Temp is 25degree), the output voltage becomes abnormal and eventually dropping down to 0V. Why?

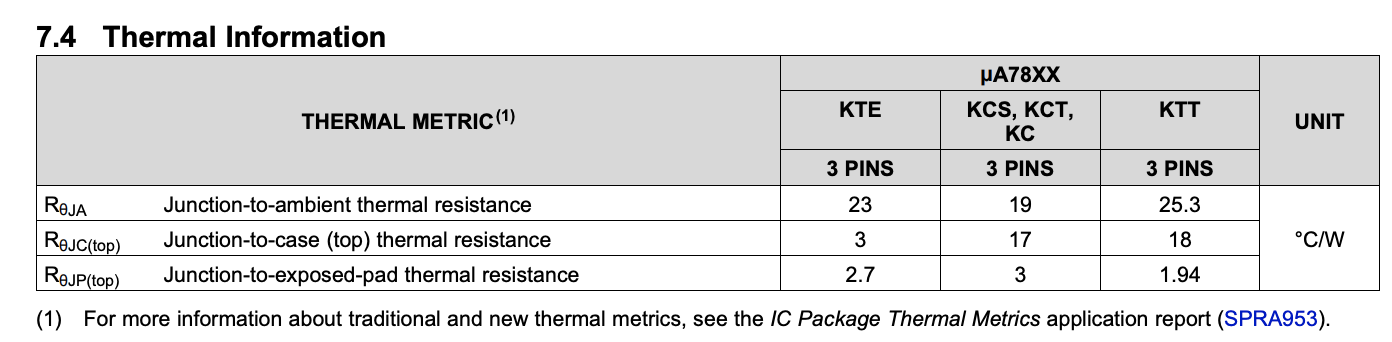

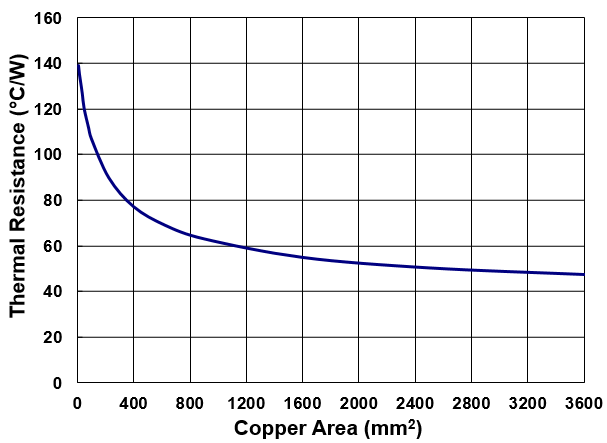

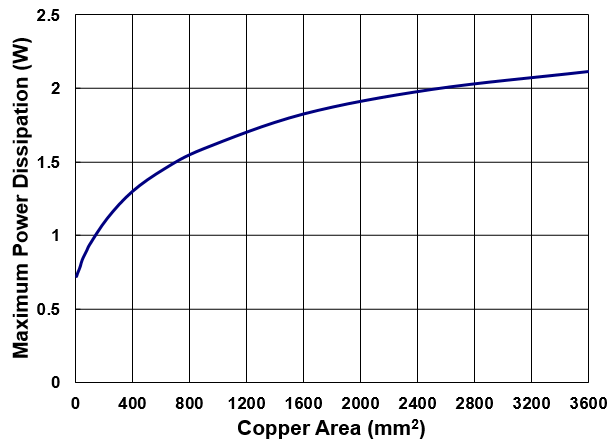

In the d/s, it says the there is coming with Internal Thermal-Overload protection. What's the triggered conditions? What's the max. power rating on chip?

Please see the tested waveform here.

Please help on this problem. thanks.