Other Parts Discussed in Thread: TPS62866

Hi Team,

Here is one question from customer.

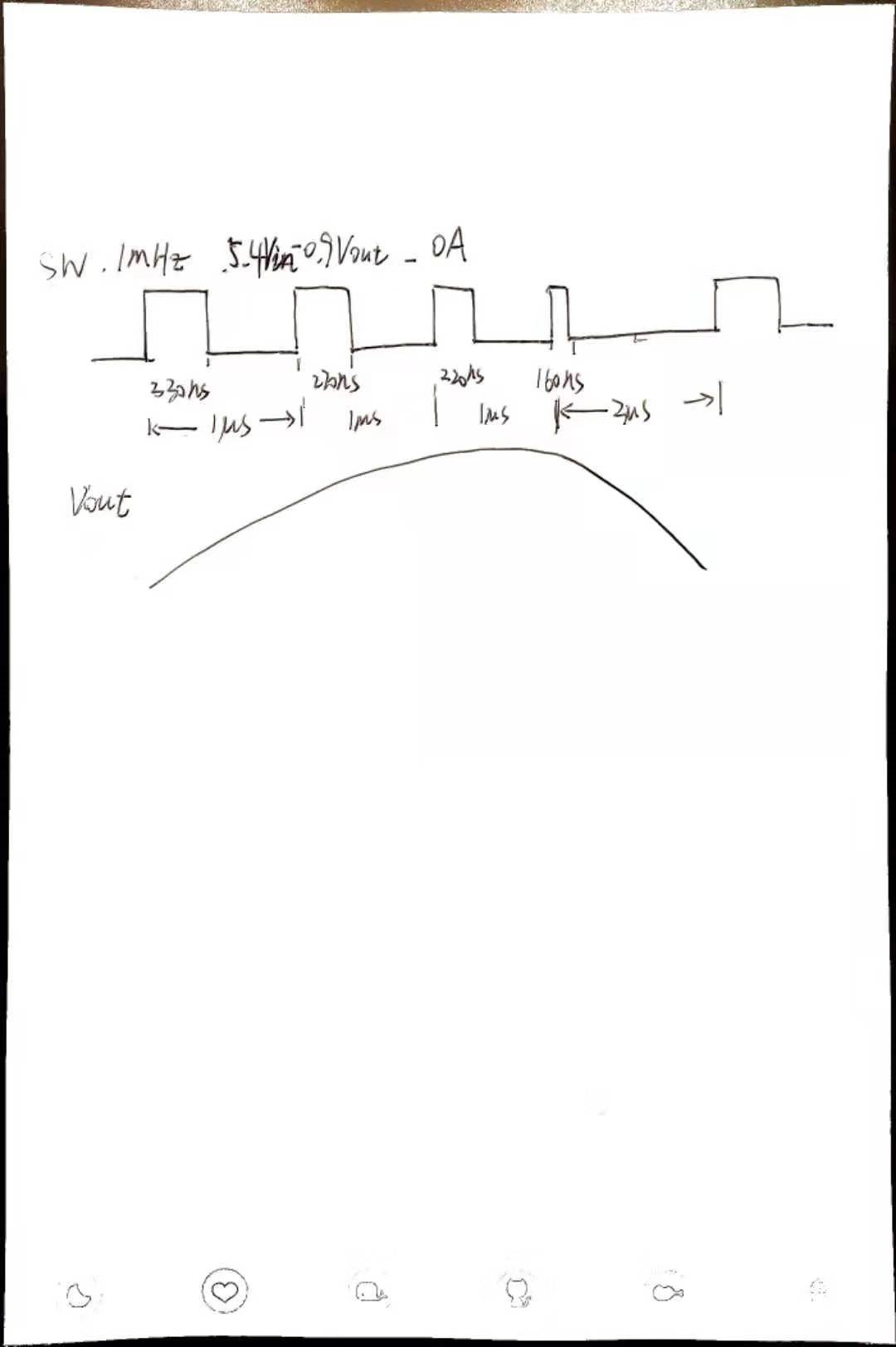

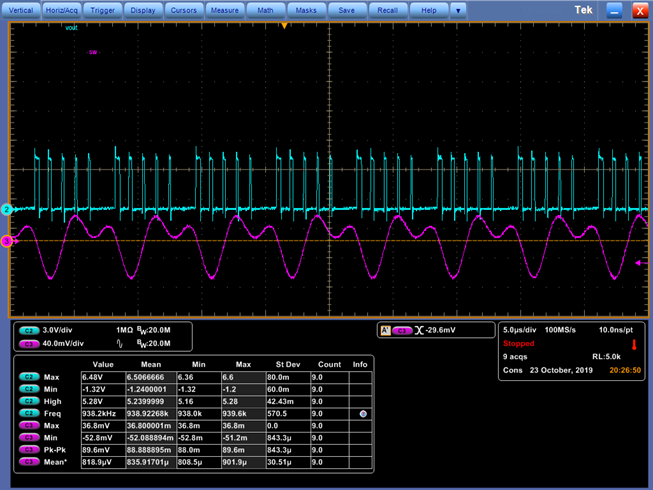

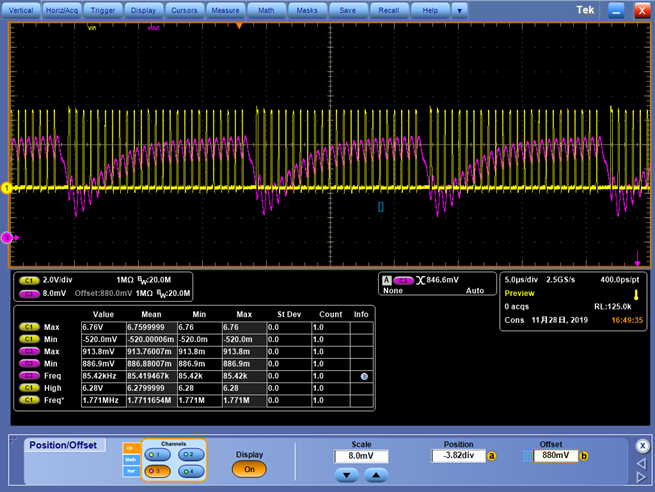

5.4Vin to 0.9Vout, Iout=0A, Fsw=1MHz, you can see below SW waveform that Duty cycle changes.

a. increasing load to 1A, Duty cycle becomes stable.

b. change Vout to below 0.9V, the issue always there. Change Vout to high value, for example, 1.2V, no issue.

c. add 15pf cap on comp pin to gnd, Duty becomes stable.

d. decrease Vin below 5.4V, Duty becomes stable.

So it seems the issue is related with Duty. I suspect it's related with noise on comp originally, but it cannot explain why there is issue with higher Vout and lower Vin. From the waveform, it seems related with Ton-min, but not sure how to explain the waveform.

Please kindly add your comments. Thanks.

BRs

Given