Other Parts Discussed in Thread: ISO7831

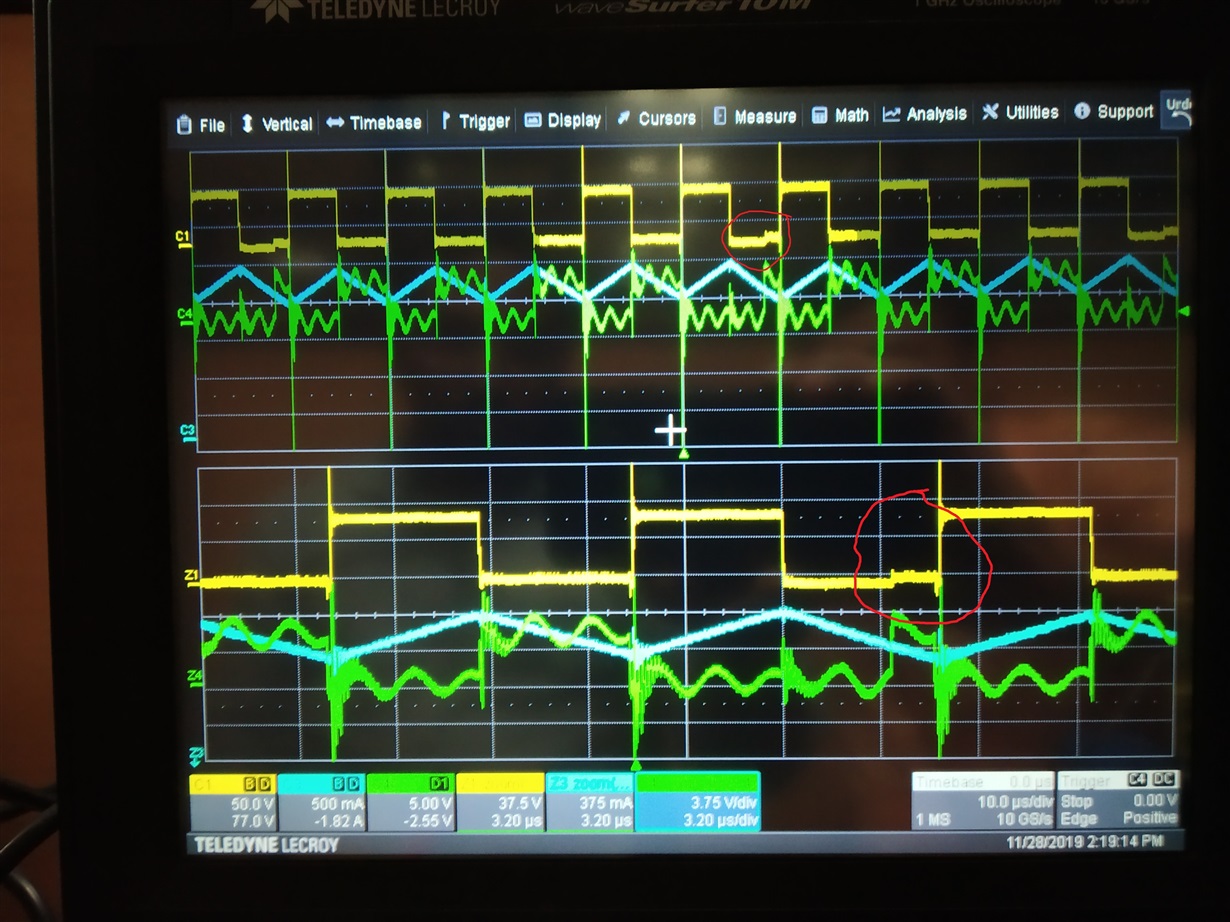

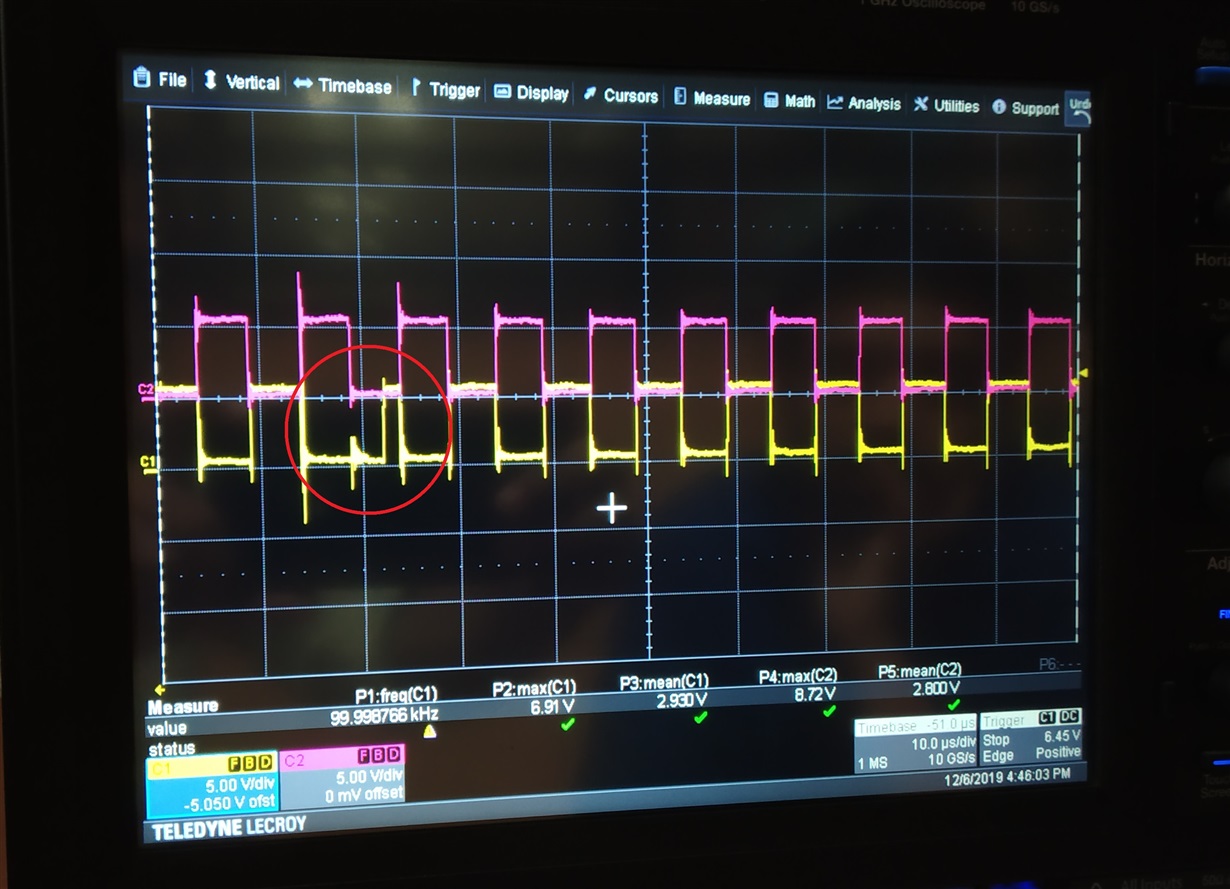

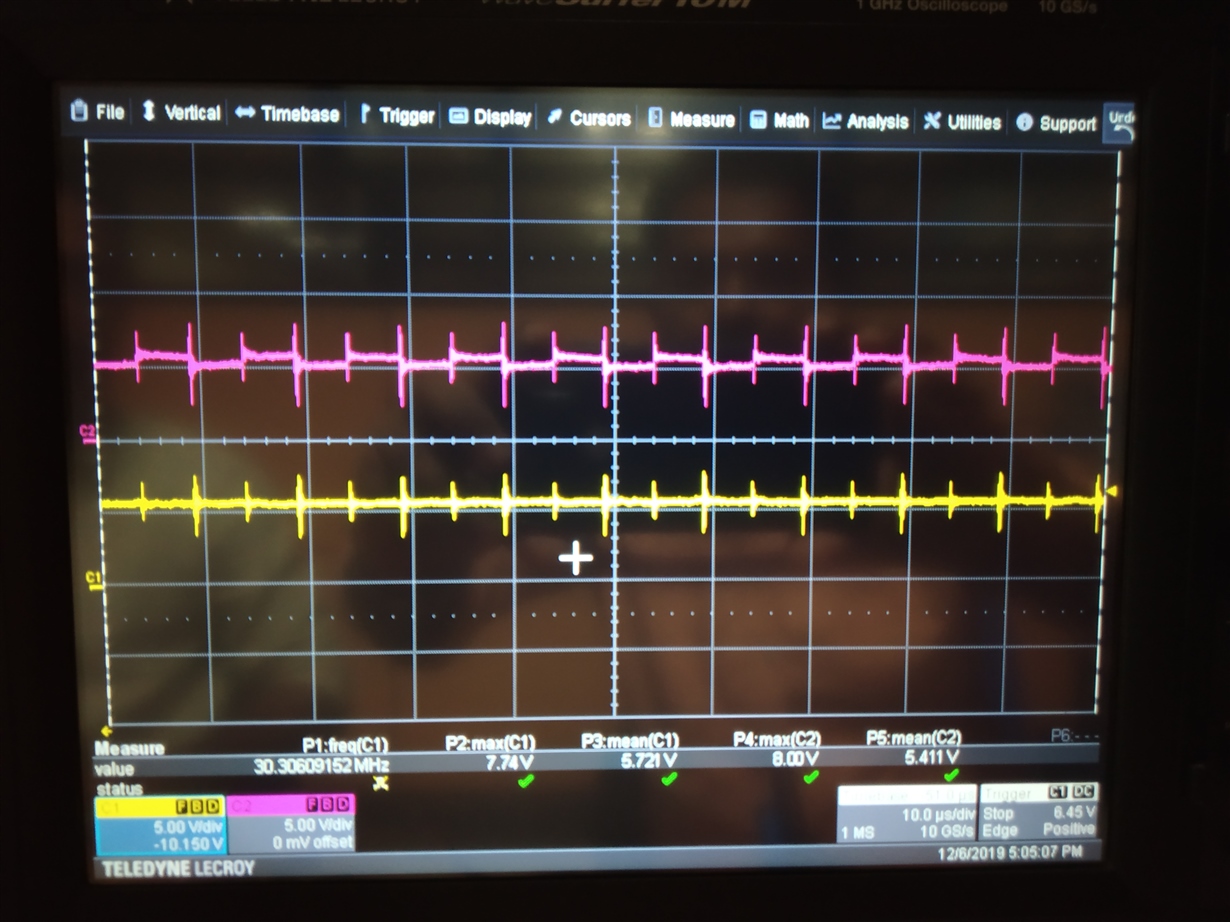

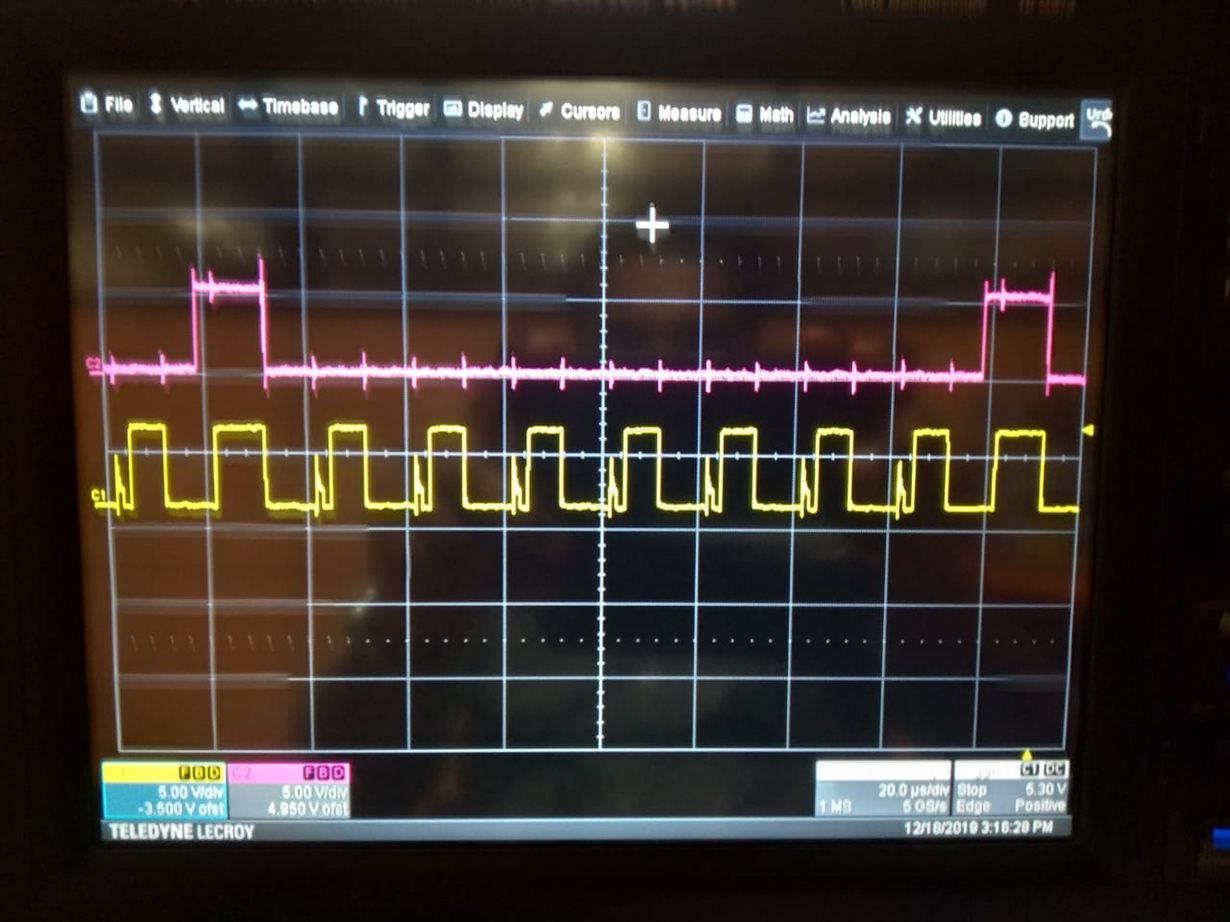

We designed one half bridge module using LMG3410RO70 using the reference from TI. We used it for synchronous boost converter operation. We tested it with open loop configuration. It was working fine when the input voltage is below 30V. But when we increase the voltage above 30V the upper device is not properly switching on and by further increasing 10 more voltage the upper device failed (not getting the 5V from LDO inside the GaN device). Please find the attachment for GaN half bridge schematic and Device voltage waveform. In the wave form you can see that there is a shift in the voltage level during turn on.