Hi,

Customer's project requires class 8 power control of 75W. Customer sets the Power Policing register and it dose not work. The load power is greater than 75W, and PSE dose not cut off. It would cut off until 90W.

Could you give a guider or suggestion for power policing setting? Thanks a lot.

1. Customer's code:

//CLASS8

else if(CLASS_8_4P_SINGLE == s_classifStatus)

{

ret = tps_SetDeviceOperatingMode (addr1, OPERATING_MODE_SEMI_AUTO, OPERATING_MODE_SEMI_AUTO, OPERATING_MODE_OFF, OPERATING_MODE_OFF);

ret = tps_SetDevice4PPowerAllocation(addr1, _4P_90W, _4P_90W);

ret = tps_SetPortILIM(s_sysChanNum, _2X_ILIM_FOLDBACK_CURVE);

ret = tps_SetPort4PPolicing(s_sysChanNum, 150);

ret = tps_SetPortPower_4P(s_sysChanNum, TPS_ON);

}

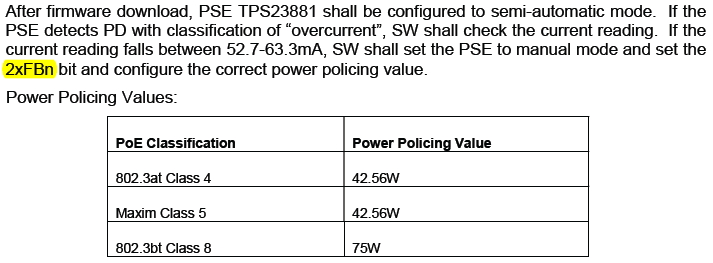

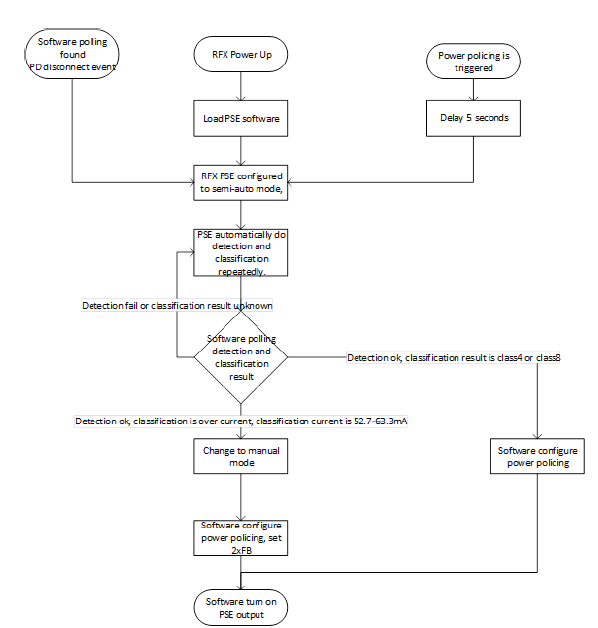

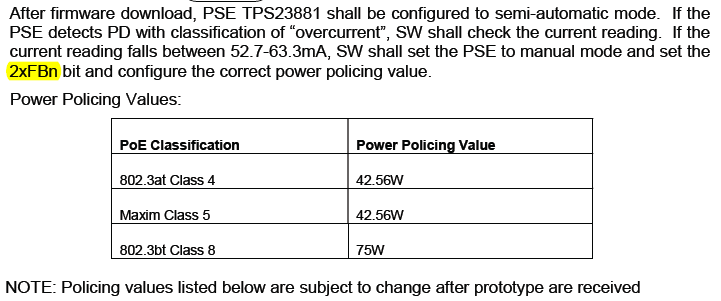

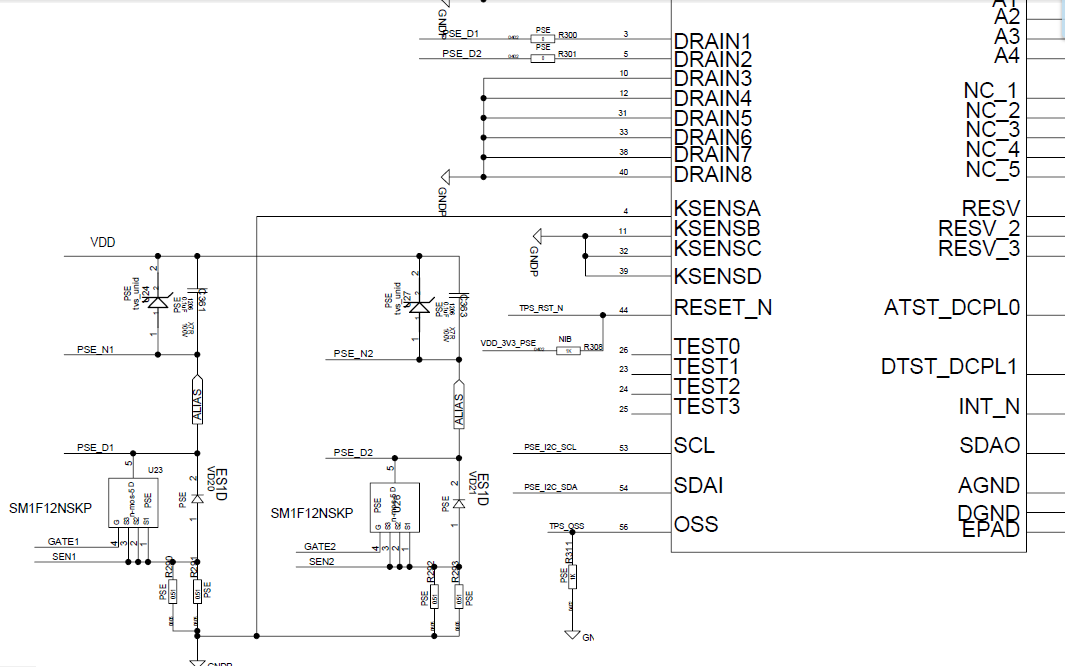

2. customer's design target:

Oliver Ou