Hello

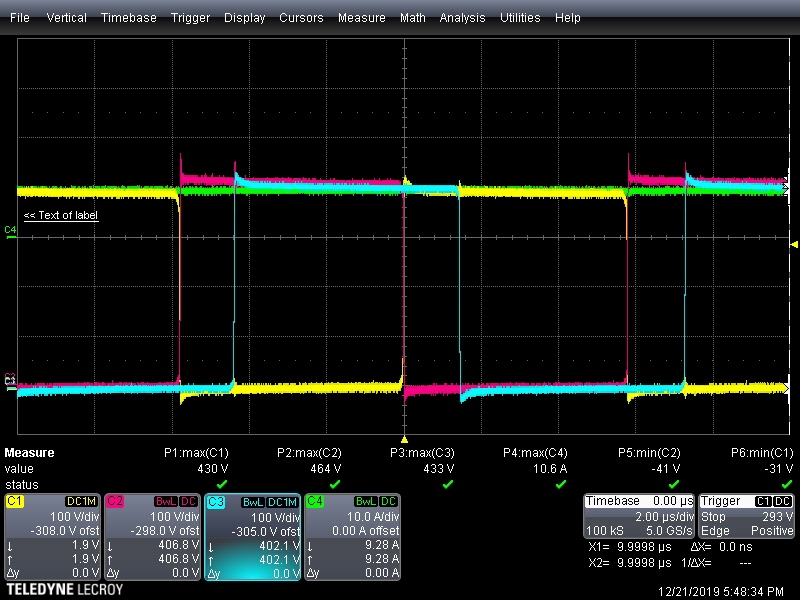

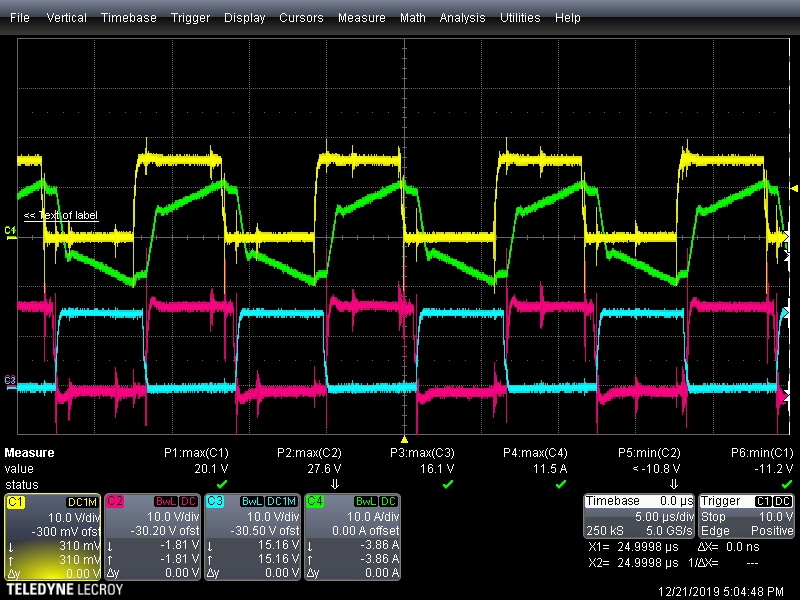

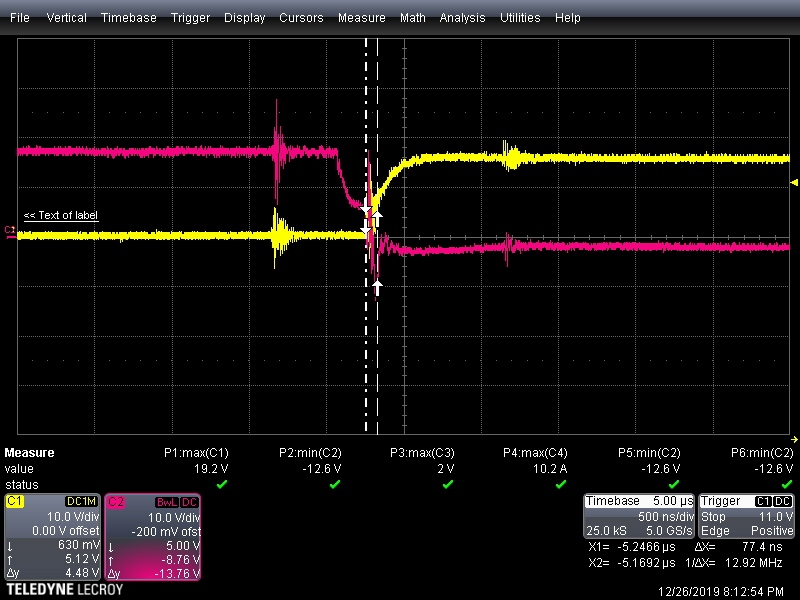

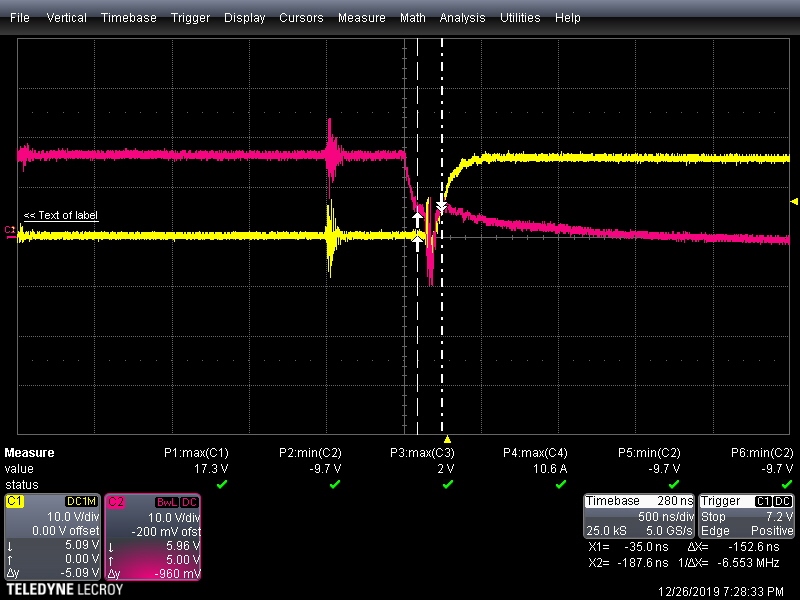

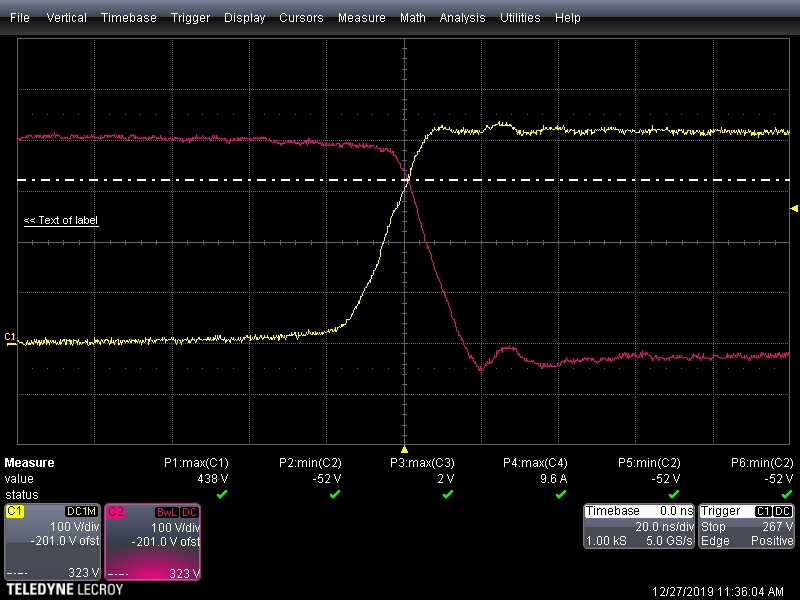

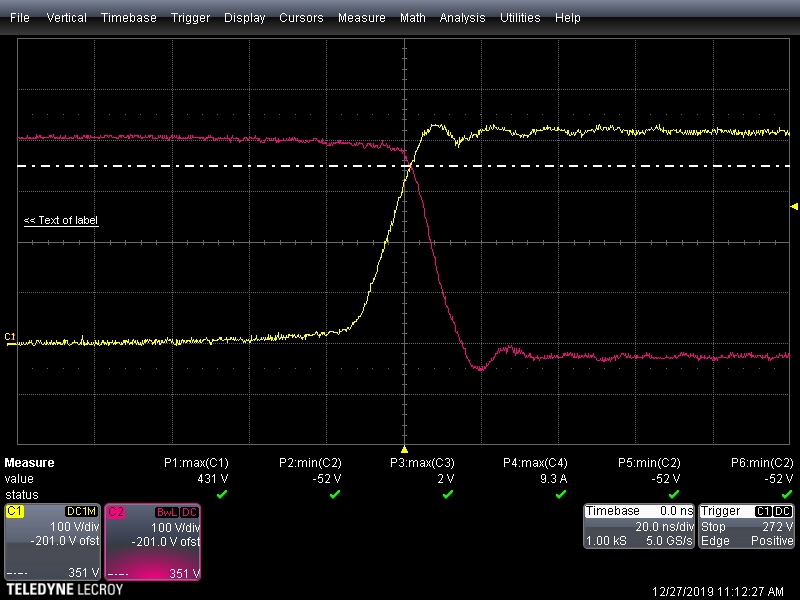

We are developing smps using UCC28950. We maked sample 200 set . but some sets are break down for aging. Almost 20set

I discovered demaged fet. So plz check some waveform.

I think there are some problem such as no deadtime , current waveform. maybe

output power : 1.8k , 53.5V 38A

topology : phase shift fullbridge

C1: Q2 VDS

C2: Q1 VDS

C3: Q2 Vgs

C4: It transformer current.

thankyou