Hi,

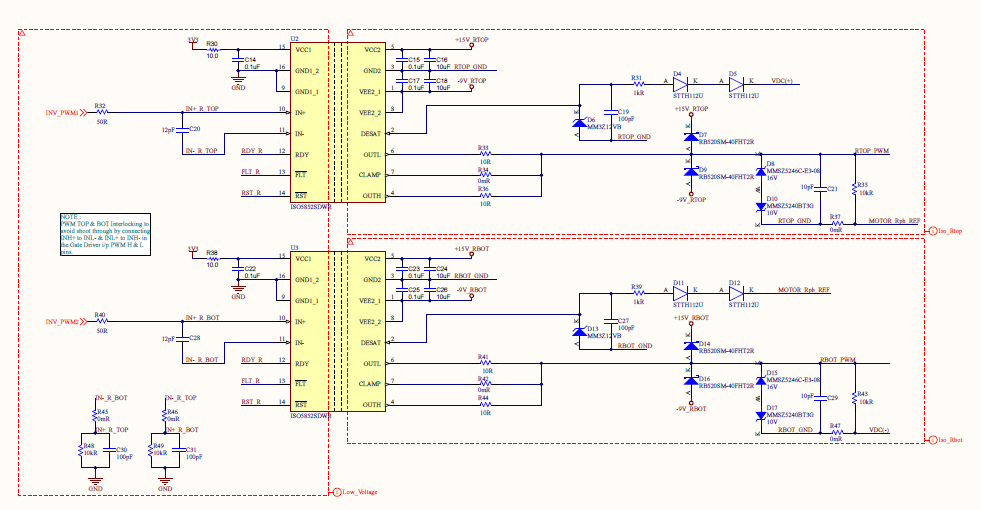

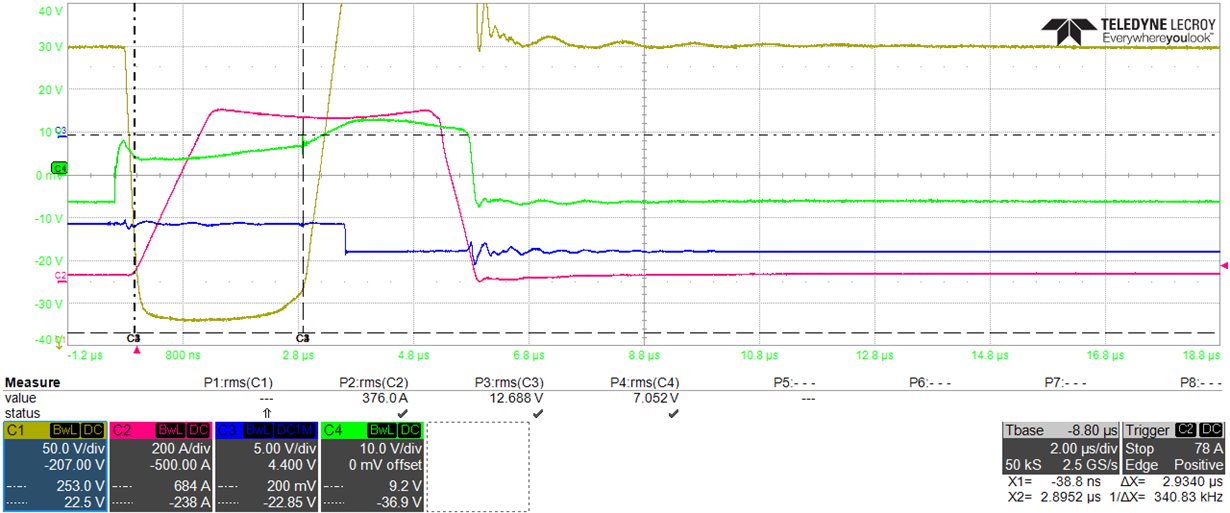

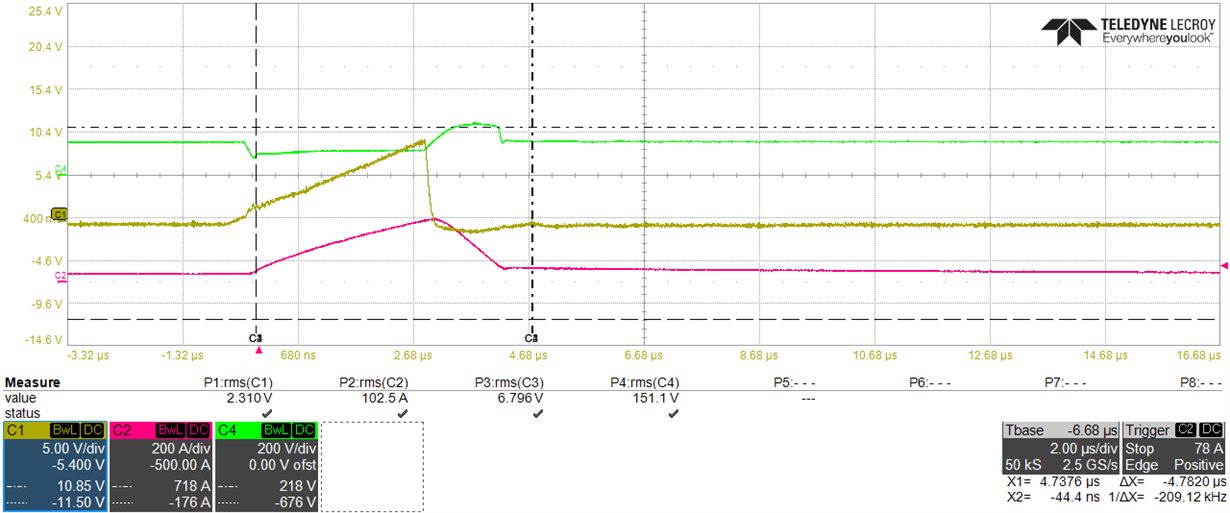

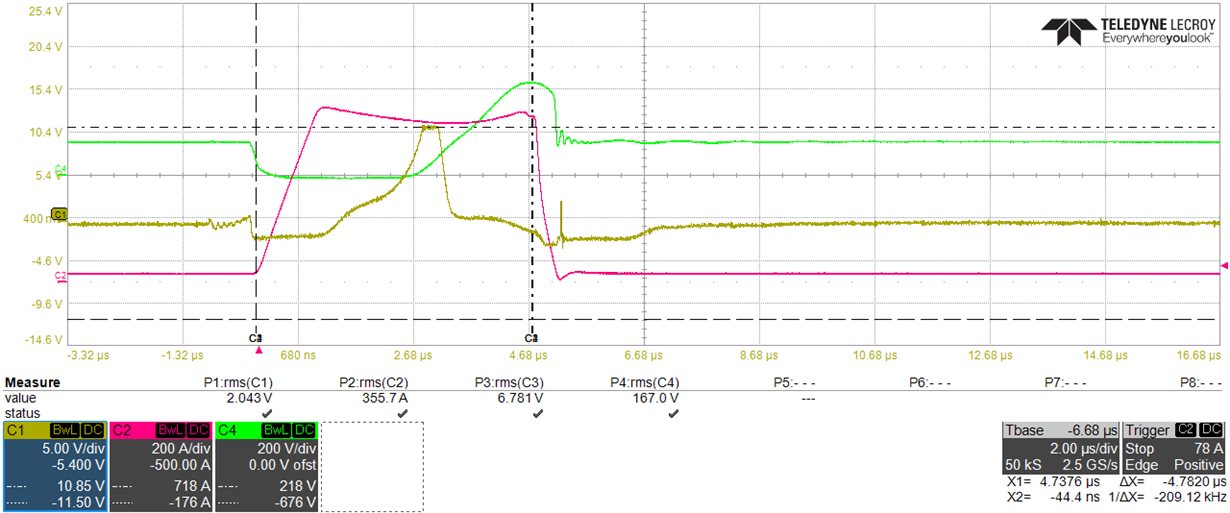

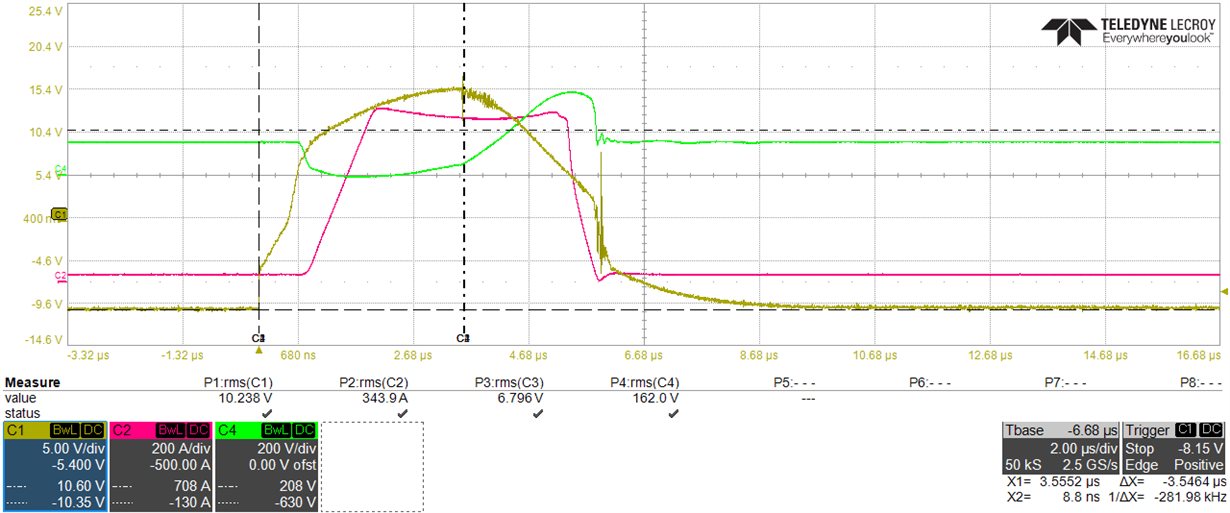

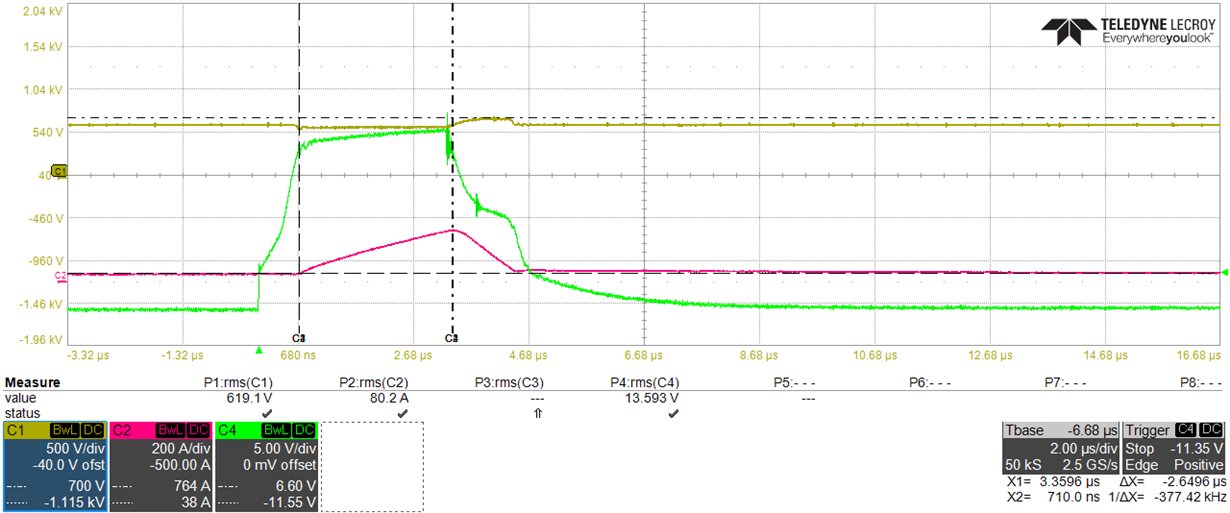

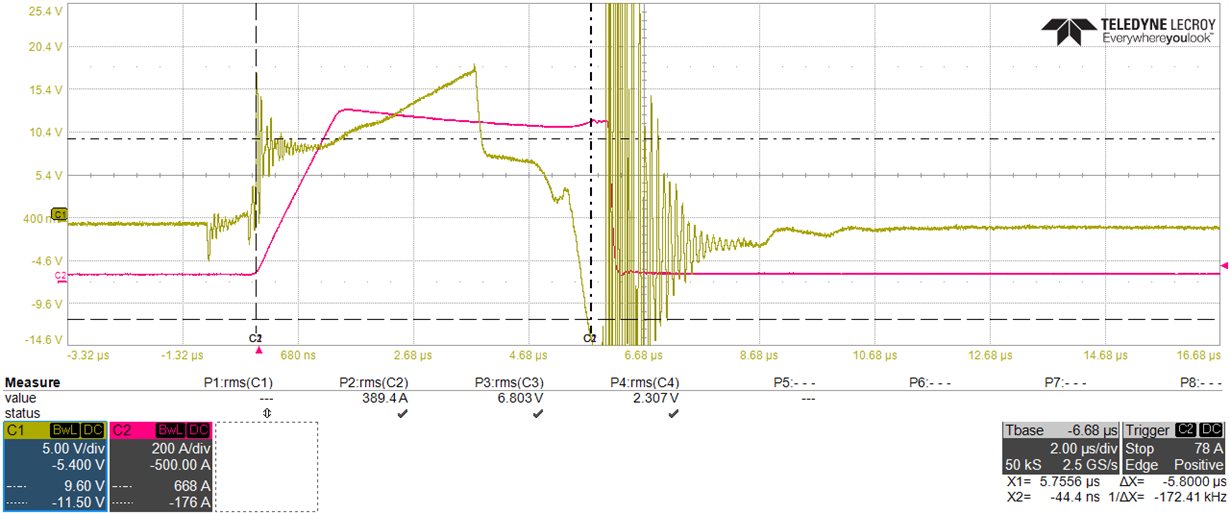

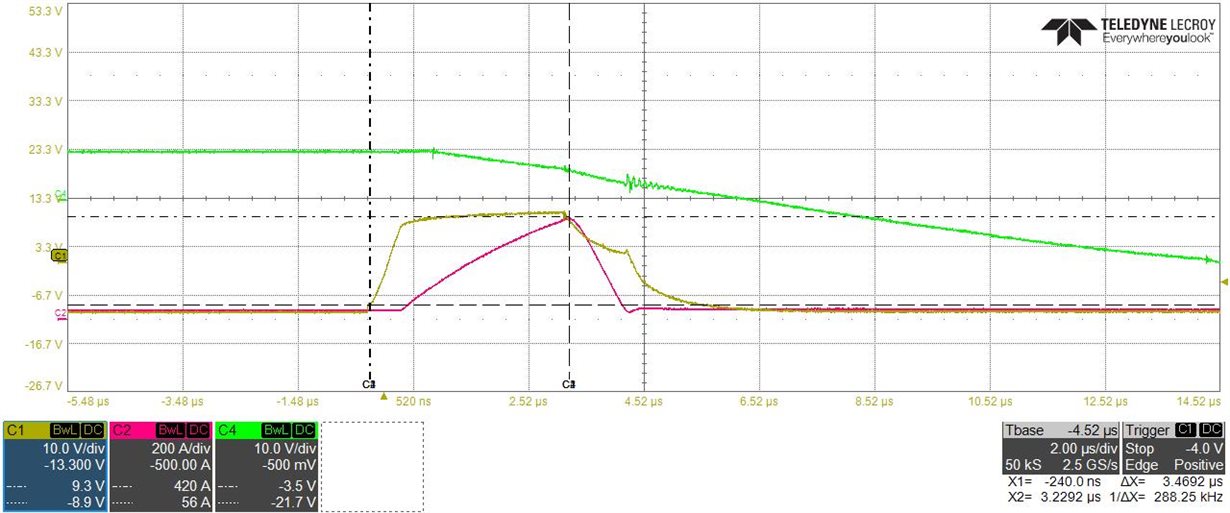

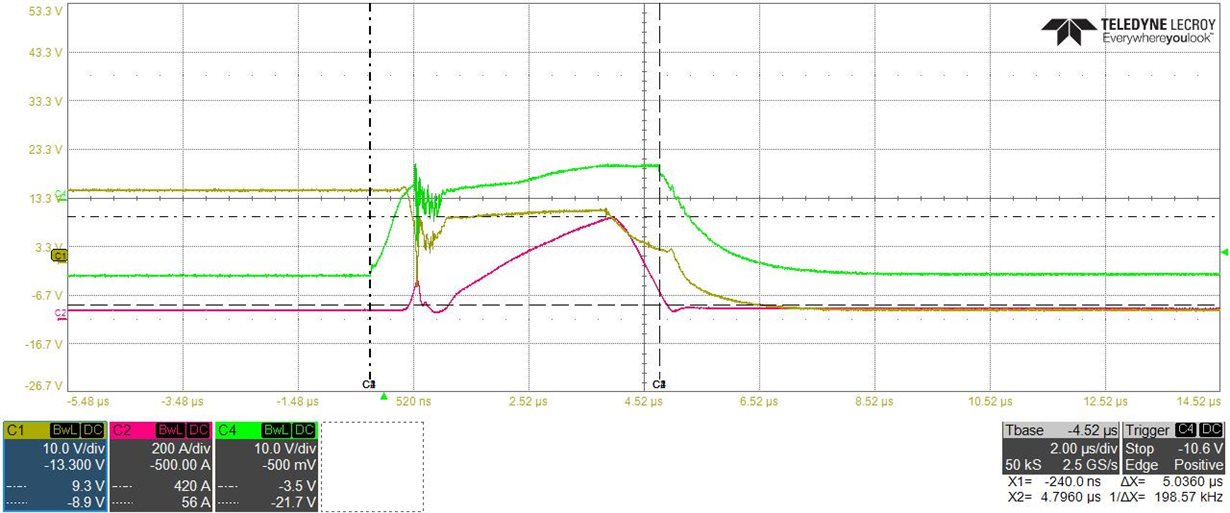

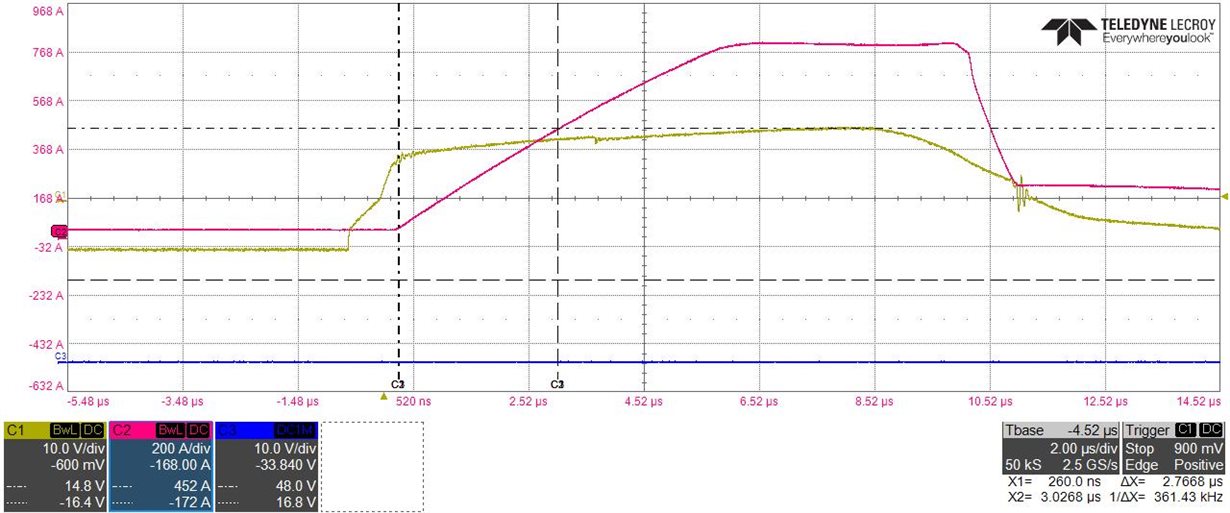

I am using ISO5852S for a IGBT Short circuit test. A DC Link voltage of 350-500V is given directly across one IGBT and made that IGBT ON. I have found even though primary side fault signal is made low. The gate emitter voltage doesn't reduce and hence the soft turn off doesnt happen. After Fault detection I had observed a DC link raise is occuring. What may be possible causes for Soft turn off not to happen ???