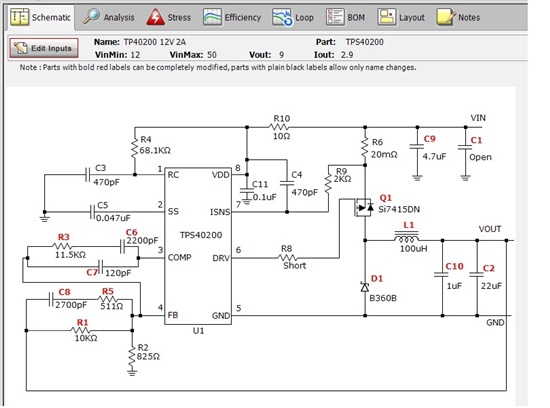

I am having a problem with a circuit that uses the TPS40200. I used SwitcherPro to design a 9V power supply with the following inputs:

Vin Min = 12V

Vin Max = 50V

Vout = 9V

Iout Max = 2.9A

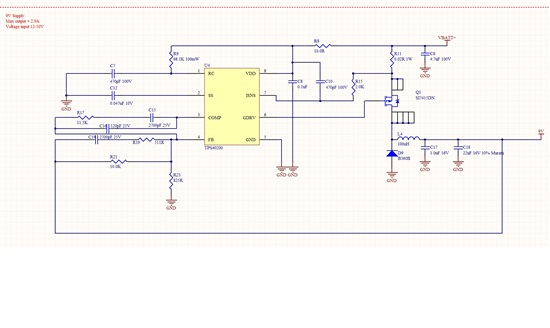

SwitcherPro gave me the following circuit, which I duplicated into my schematic:

I am using the TPS40200 to step down a battery voltage of approximately 24V down to 9V, which then goes into a series of cascaded power supplies of 5V, 3.3V, and 1.8V. The load on the 9V supply draws 0.05A. The reason Iout Max = 2.9A is because our power system is designed to supply auxiliary power to external user-supplied devices which are of an unknown resistive load.

The problem I am experiencing is that this 9V power supply draws 0.2A at 24V, even when I have disconnected the output of the 9V supply to the cascaded power supplies and their loads. This is a much higher current draw than I expected. I measure 0V at the output. The cascaded power supplies below the 9V supply all work when powered from an external supply, so I am led to believe that it is a problem with the TPS40200 circuit.

When I measure the resistance between Vin (24V) and GND, I get approximately 150K. Is this value expected? I am concerned that I have a short somewhere. I have attempted to remove components to determine the source of the short, but so far, only the removal of the TPS40200 itself changes the resistance between Vin and GND.

Is there a minimum current draw requirement for this circuit to function? The datasheet does not indicate a minimum, but SwitcherPro says that Iout Max ranges from 0.1A to 3A.

Any help would be greatly appreciated. Thank you very much in advance.

Sincerely,

-Kim