How can I achieve good heat rejection of Power MOSFET CSD19535KTT with D2PAK package?

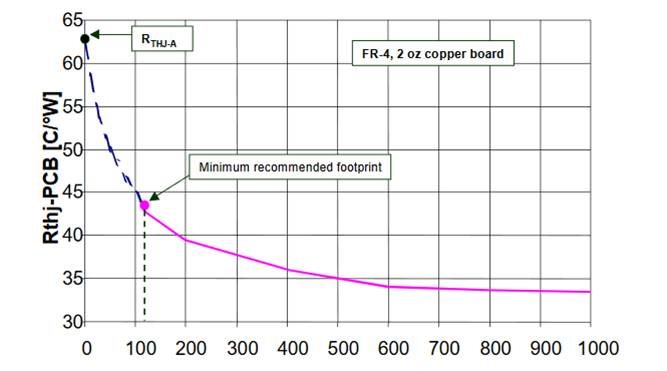

While comparing to the base area of MOSFET, I am increasing the copper area on the PCB like 10%, 20%, 30% and so on.

while doing like that when i can get the good heat rejection point? Also i wanted to know how i can find the saturation point of heat rejection when we go on increasing the area of copper deposited on the PCB.

what are the effects of Heat transfer when the area of copper on the pcb is increasing?

Regards,

Jnaneswar