Dear sir,

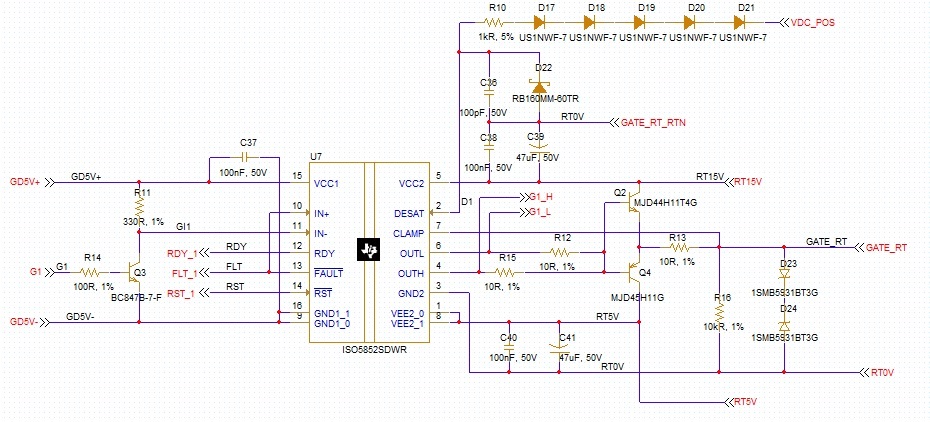

we are using ISO5852S for our inverter gate driver. Our circuit is given below.

When the IGBT was failed (desaturation was disabled) gate - emitter was damaged. 1SMB5931BT3G was damaged.

It damages the ISO5852S driver also. Short-circuit was happened between the pin numbers 1, 5, 6 & 7.

Is it possible to protect the ISO5852S during gate - emitter short circuit condition.

Thanking you.

Thanks & regards,

Rajasekaran.