Hi,

I have made a high power design with the TPS40422 operating in 2 phase mode. I have chosen a inductor with a L of 200nH and Rdc of 0.29mohm. I designed the TPS40422 to supply 35A per phase for a total of 70A in the 2 phases. When i am testing the part, i am using TI's Fusion Digital power designer to display the output current. I have adjusted the IOUT_CAL_GAIN to a value that is the closest to the 0.29mohm of the inductor resistance and also increased the IOUT_OC_WARN_LIMIT and IOUT_OC_FAULT_LIMIT to 45A and 49A retrospectively.

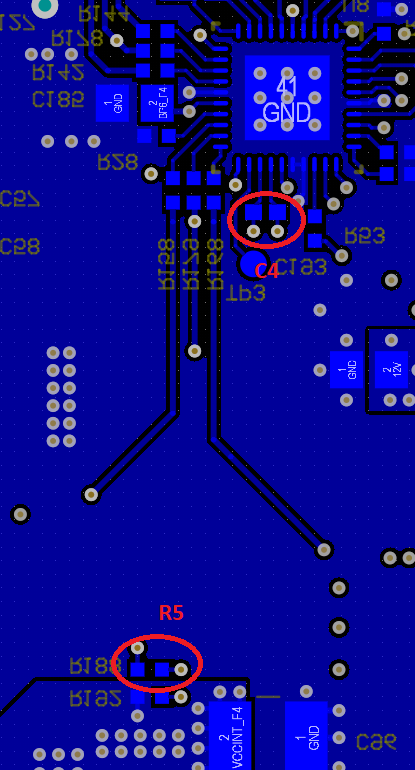

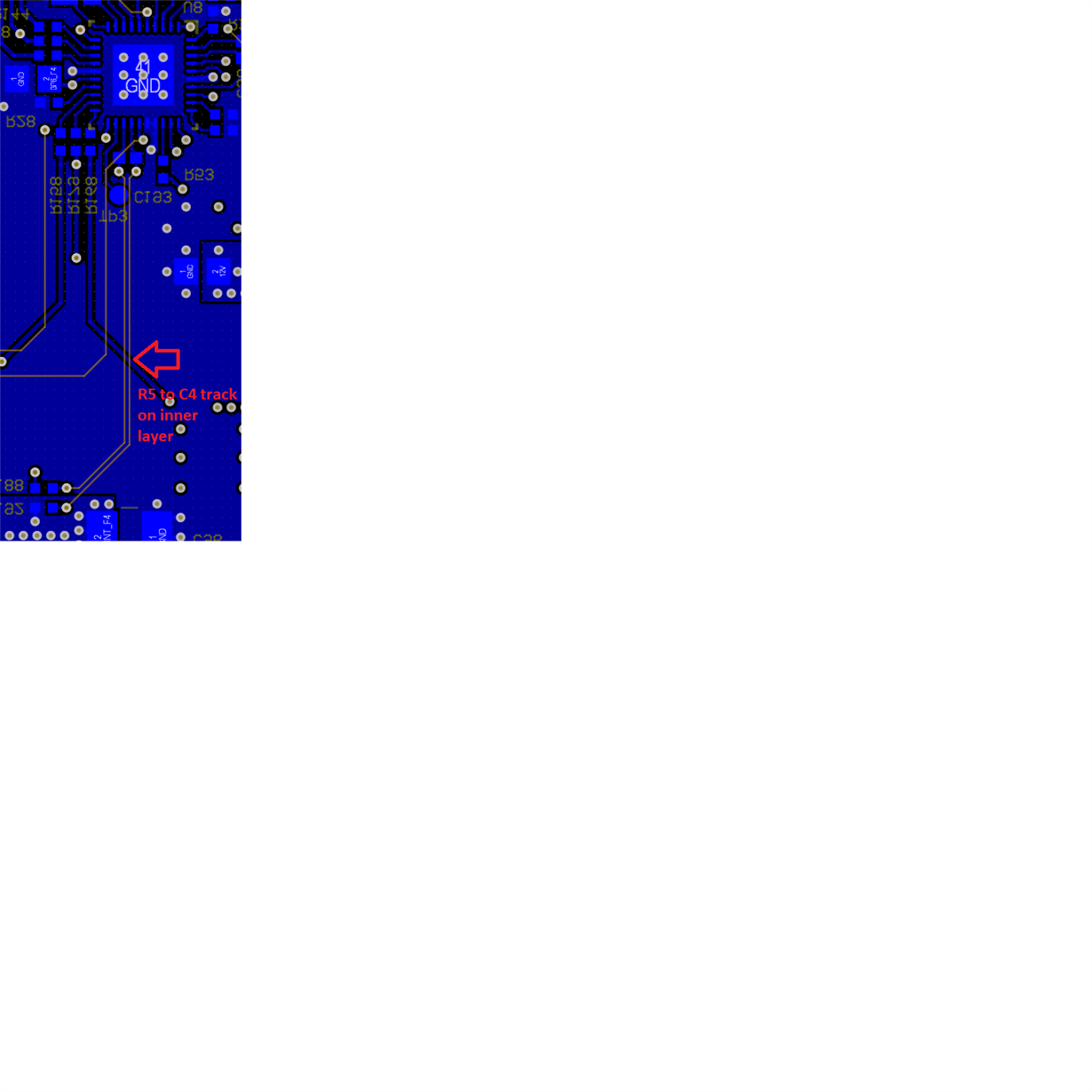

In my testing, i increased the load on the TPS40422 and at about 28A output (per phase as displated by the TI's Fusion power designer), i would get a IOUT_OC_FAULT_LIMIT and it would shut down the output voltage. I tried different values of R5 and C4 as per page 16 of the data sheet and it made no difference. In the end i settled with R5 = 1.5Kohm and C4 = 470nF which satisfies equation 2 on page 16 of the datasheet. I'm not sure why the part is shutting down as the IOUT_OC_WARN_LIMIT and IOUT_OC_FAULT_LIMIT is well beyond the displayed current draw.

In trying to figure this out, i increased the value of IOUT_CAL_GAIN to double of the inductor resistance and i am able to draw about 30A per phase without tripping the IOUT_OC_FAULT_LIMIT.

Can you please provide some guidance as to why the TPS40422 is tripping the IOUT_OC_FAULT_LIMIT and shutting down the output voltage when it is supplying less current then the set tripping point?

Thanks