Other Parts Discussed in Thread: BQ76952,

Hi!

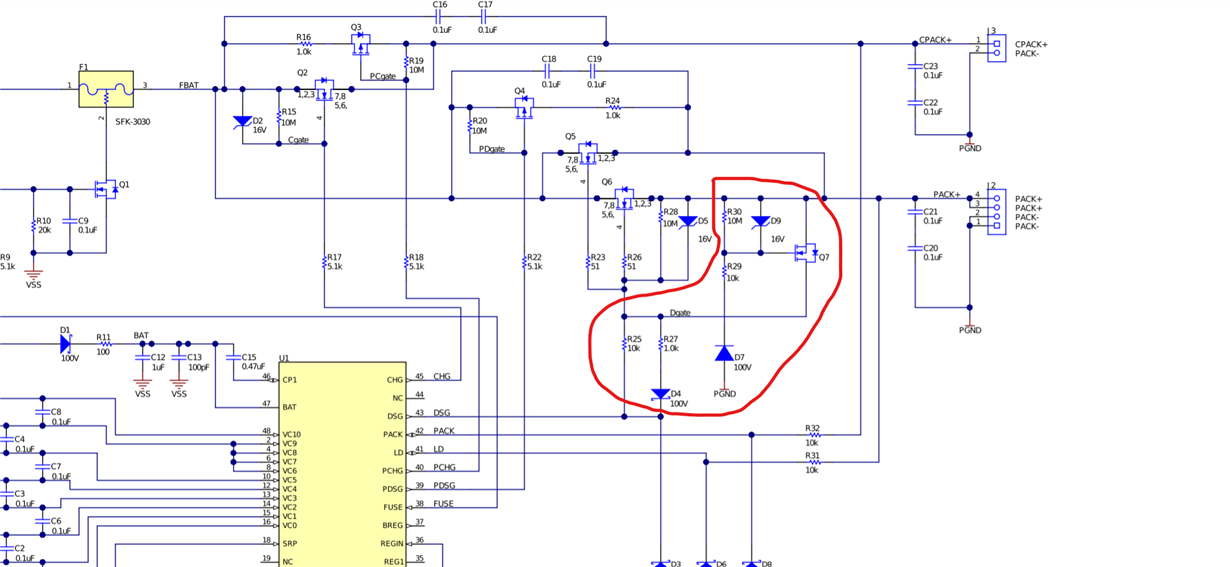

I was looking through the "Parallel Paths with the BQ76952 Battery Monitor Family" application note (http://www.ti.com/lit/an/slua952/slua952.pdf) and in the Parallel FET Schematic (page 3), I'm curious what this part of the circuit does/what are the complications of omitting this.

Thanks in Advance!