Peter

I made the modifications,using a bench with a variable resistor as Load i can get the system working till 6 Amp at 14Vout this means 7*14=84 Watt.

I put in and take out the load the system is working correctly.

But, my load is a full bridge as You can see in the schematics that is driving two pulse transformers. each pulse transformer is a 1:1:1:1:1 so one primary 4 secondary, each secondary drives in X 3 fet each each fet is a rafly 20nF gate capacitance. the main inverters switches from 1kHz in PWM ZCS when loaded at lighest power continuous mode to 20kHz always in PWM ZCS high power continuous mode, anyway in continuous mode the load is very light also because for the 12 Vdc power supply the frequency of working is low.

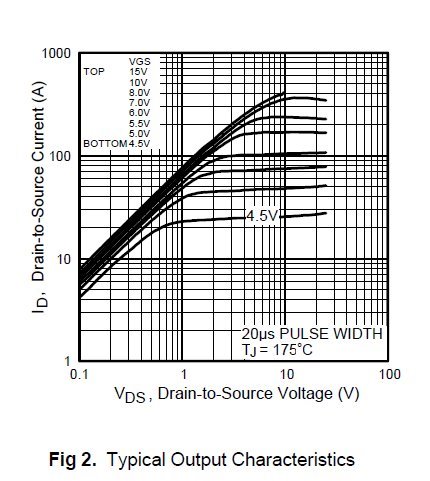

When the system is working in discontinuos mode the highest frequency can be 220kHz and the run can be at least 6 seconds and after stop So the worst case for the 14 Volt PWs is when it runs at 220kHZ; so for each fet of the inverter we need a power given by the equation

CV^2 * Fsw so P= 20*10^-9*(28^2)*220*10^3= rafly 3.5W

so 24 fet to be driven P=24*3.5=84W

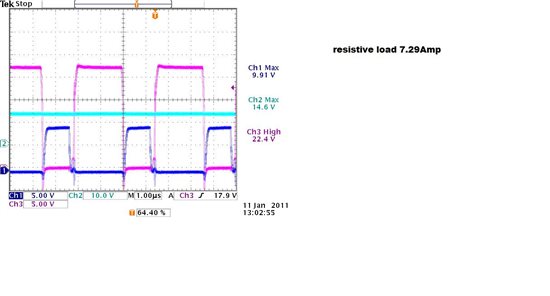

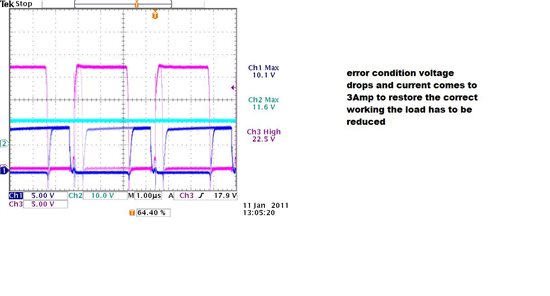

That is the power I get out with the resistive load. Now, when i load the 14 Vdc PWs with the ''BRIDGE LoAD'' the PWS in 100us start with the one pulse long one short the out voltage drops at 10 volt and till the load is applied the system works in this way.

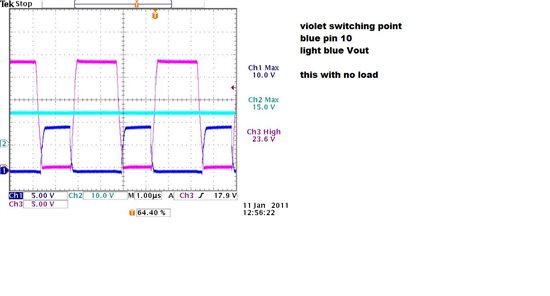

Bu looking at the switching point what i do not understand is, by changing from no load condition to load coundition the waveform at the switching point is nnot enlarging the

working duty cycle but is changing a litte bit the shape it becomes from a pseudo trapezoidal to a quasi rectangular

as showed in the pictures

What can I do? where i'm wrong regards mganzetti