We are using the LMG1205 bootstrap gate-driver for driving EPC2020 GaN transistors, and we seem to be facing what looks like a ‘latch-up’ issue, resulting in our GaN transistors blowing up. We suspect that this is related to the high oscillations during soft-switching transition, at high currents. However, to come up with preventive measures, we are trying to understand what part of the LMG1205 IC is malfunctioning, and what exactly is the trigger for this latch-up-like action.

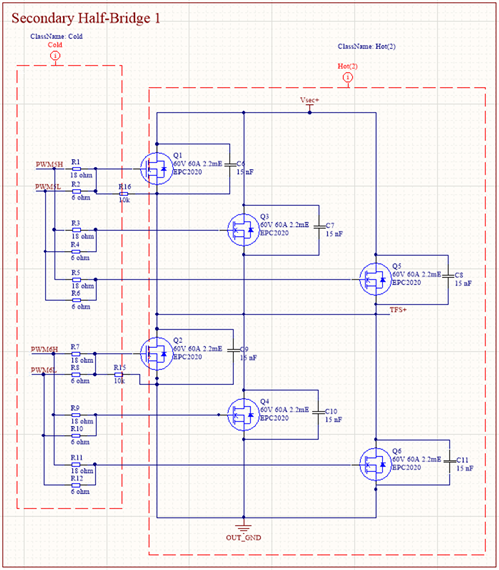

Circuit Description

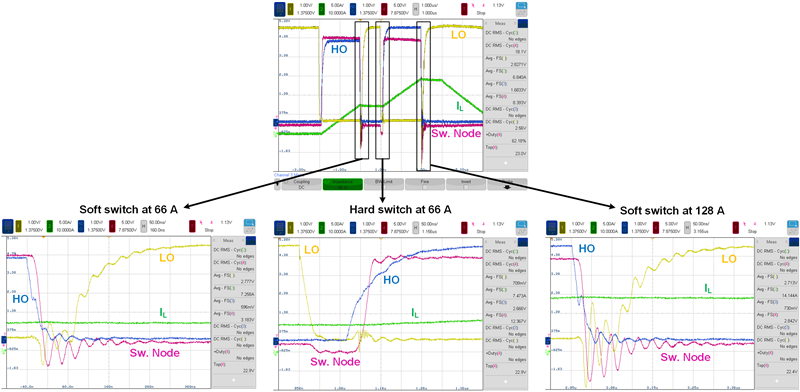

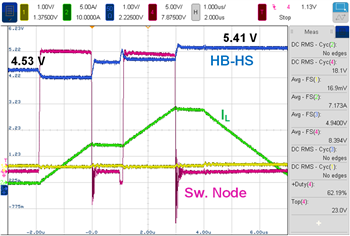

For the half bridge structure, both the high-side and low-side switches are comprised of three parallel EPC2020 transistors. Our application involves peak currents of over 200 A through the combination of three parallel transistors; the RMS currents are lower (max 100 A). Thus, at the instant of switching, the switching current can be as high 200 A. To assess the switching performance, we have performed double-pulse test for the half-bridge. While the hard-switching transitions are fairly satisfactory, the oscillations during the soft-switching transitions are much worse.

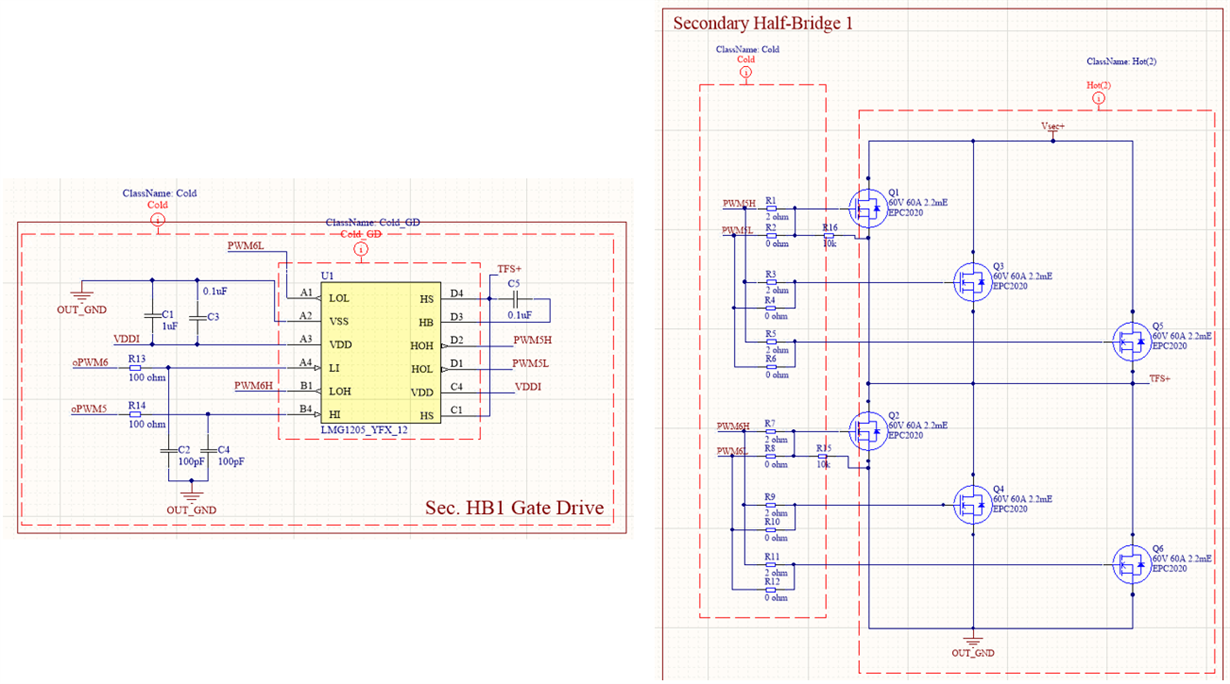

So far, we have attempted DPT at >170 A three times, with varying values of external gate turn-on resistance (10 ohm to 18 ohm), turn-off gate resistance (1 ohm to 5 ohm), and varying values of snubber capacitance (0 nF to 15 nF, per switch). On all three DPT attempts, we have encountered a failure caused on exactly one of the three paralleled transistors on the high-side. The specific transistor that fails (based on location on the PCB) has varied; however, the failure always occurs on a high-side transistor. Attached please find a schematic of the circuit being tested.

Problem Description

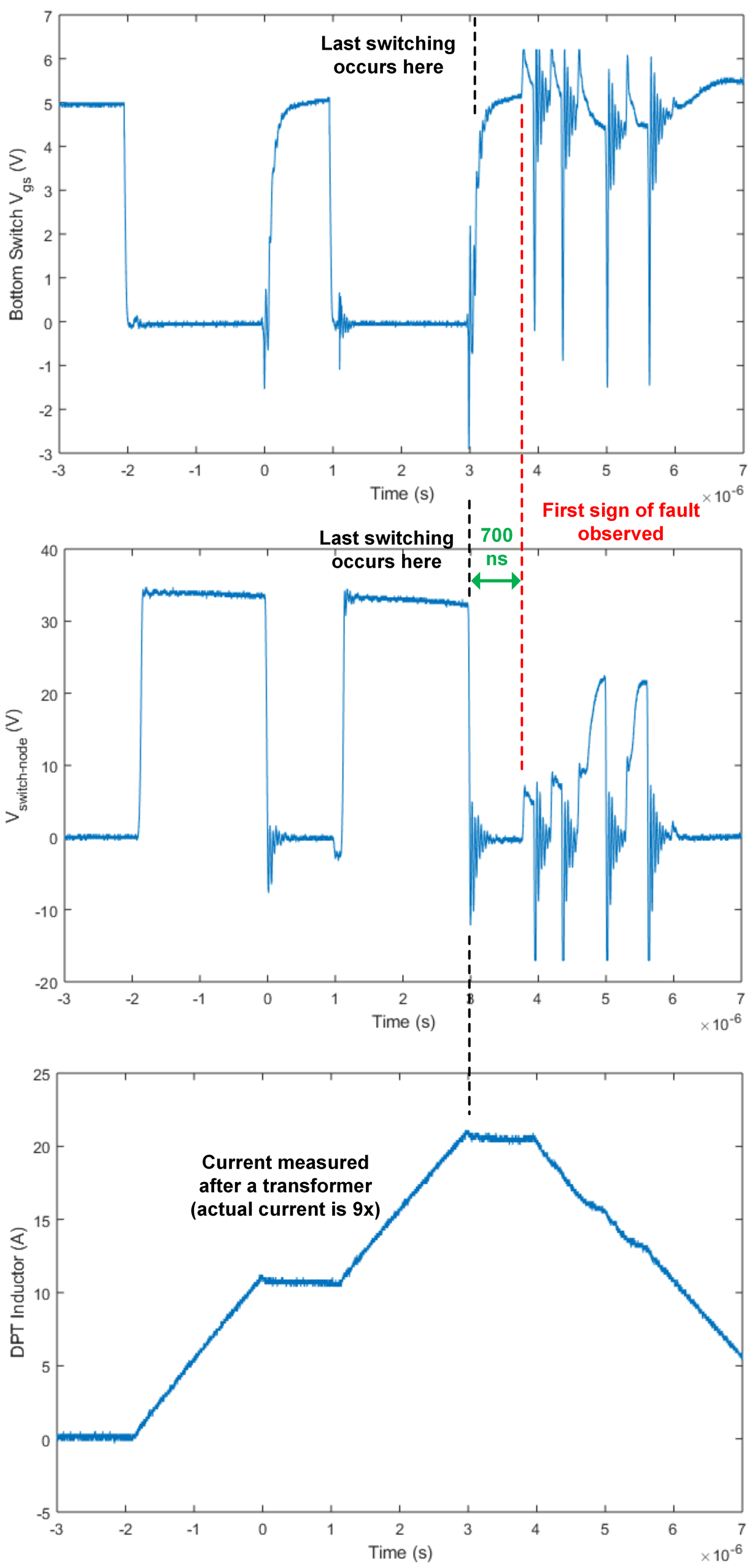

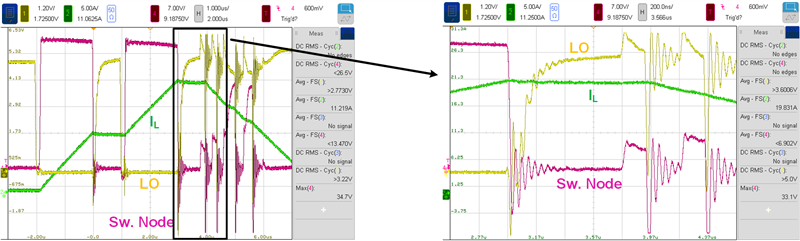

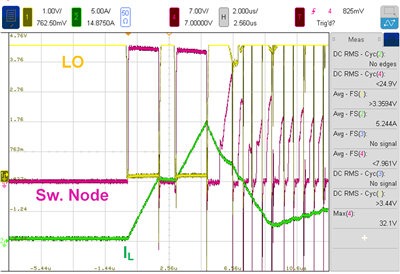

During the soft-switching transition, we found that the switch-node voltage (i.e. the voltage between HS and VSS) is having a high negative overshoot. For the circuit operation with 15 nF added snubber capacitor per switch, Rg,on = 18 Ω, Rg,off = 5 Ω, the switching node voltage seems to go below -10 for 15 ns, as measured close to the gate driver pins, as shown below in the extracted experimental data from one of the failure instants. Due to limitation of available probes and test points, the gate voltages are measured using the Keysight N2894 700 MHz non-isolated probe with pig-tail ground return, the switch-node voltage is measured using a Keysight N2790A 100 MHz differential probe. The inductor current was measured using a N7026A 150 MHz probe connected after a current transformer.

Interestingly, rhe first noticeable symptom of the fault occurs nearly 700 ns after the switching transition. Subsequently, the switch node voltage shows a periodic rise (even when the bottom switch gate is held high), and hence we are suspecting that LMG1205 is going into some sort of a latch-up mode. It appears that the top switch starts conducting while the bottom switch is still in ON condition, causing what appears to be a short circuit current to flow, and thus developing a voltage at switching node (Ids* Rds,on).

Hence, we are trying to find answers to the following questions:

(a) We could not find any details on latch-up response of LMG1205 - how does it respond to negative voltages on the Vs pin - will it pull up both high-side and low-side gate outputs to 5 V?

(b) How does LMG1205 typically respond to the negative voltage between HS and VSS pin? Could LMG1205 latch-up in this scenario?

(c) Apart from the negative voltage on HS pin, is there any other condition (undesirable voltage on some other pin) that could cause the issue that we are encountering?

(d) If this is indeed a latch-up problem, what measures could we take to avoid this phenomenon?