We have been working with UCD90120A, attempting to configure a LPGO in state machine mode with assertion/deassertion delays, but have been having a problem.

Our expected behavior is that if the inputs change momentarily, but then change back to how they were within the delay time, then the output would not change and we would stay in the same state.

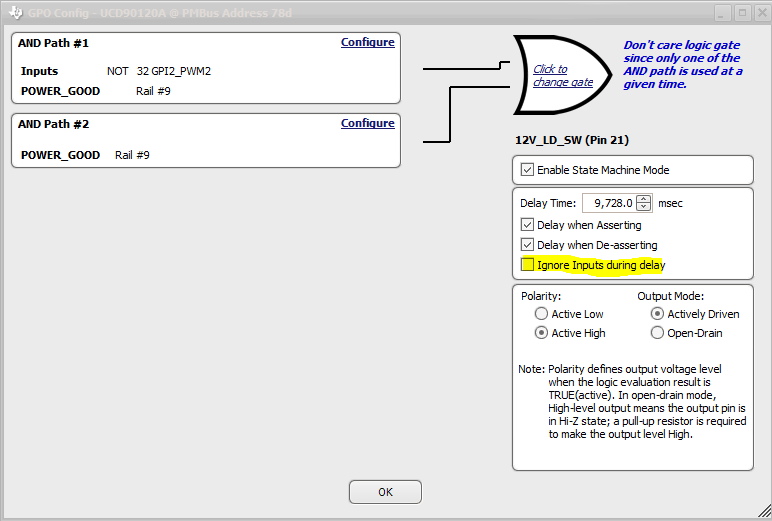

Here is a screenshot of how we have the GPO configured:

Note that "Ignore Inputs during delay" is NOT checked.

According to UCD90120A user guide, the "GPO Delays section" indicates that "On a normal delay configurarion, if the logic of a GPO changes to a state and reverts back to previous state within the time of a delay then the GPO will not manifest the change of state on the pin...A delay configured in this manner serves as a glitch filter for the GPO."

For out configuration, any signal change that doesn’t last longer than ~9.8s shouldn’t result in a change of GPO.

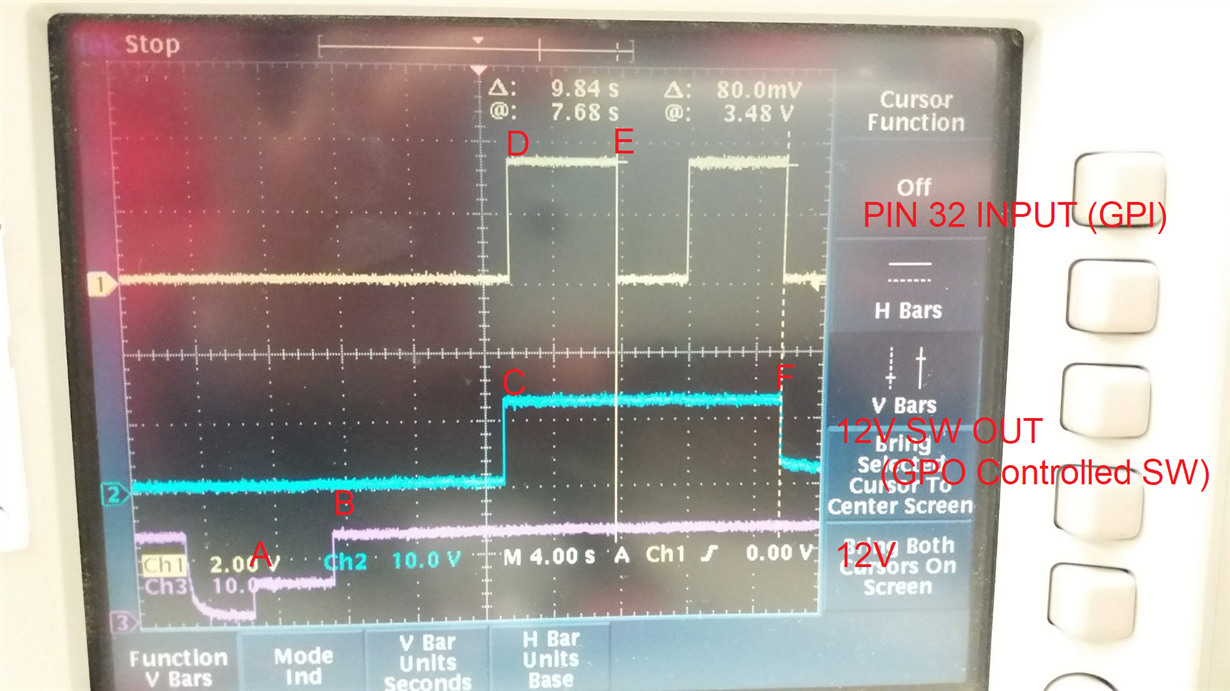

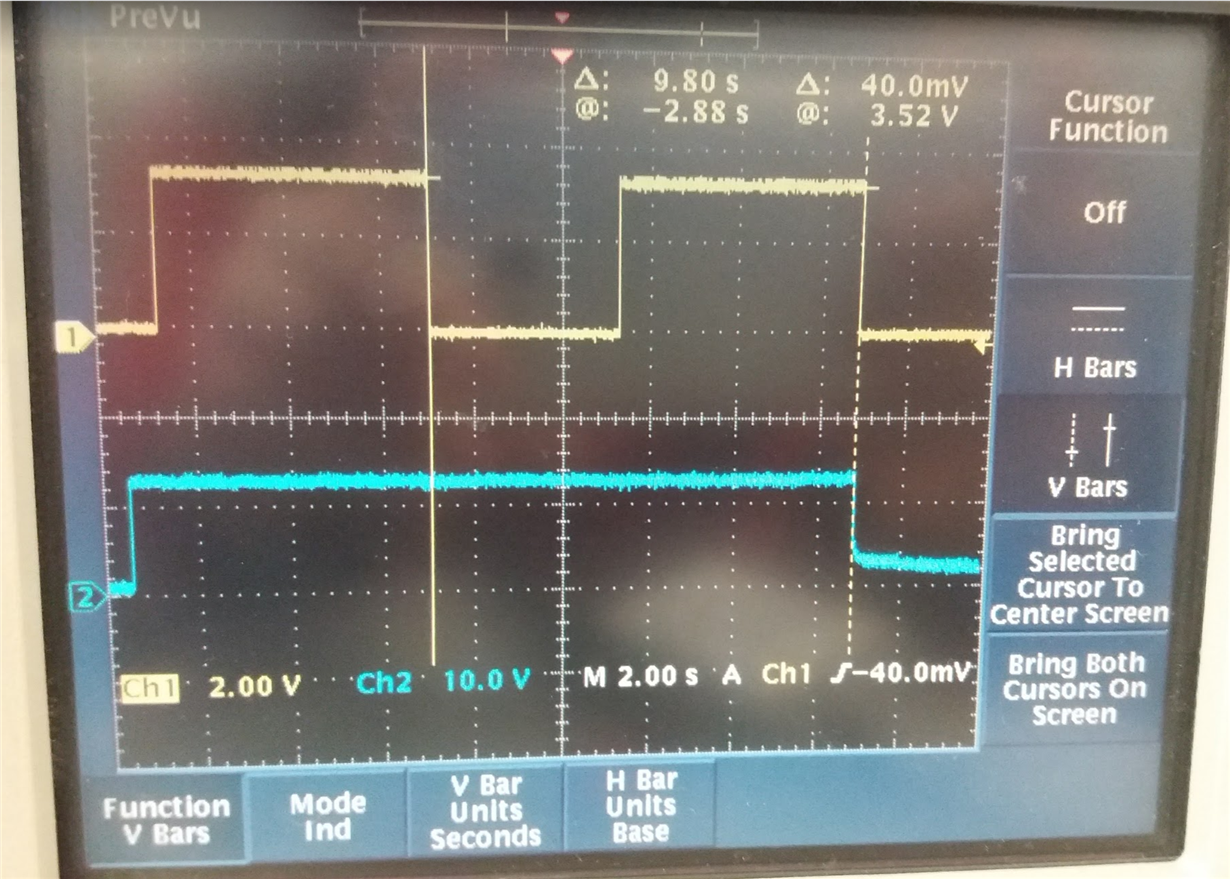

The following functionality is seen for the configuration shown above:

The yellow signal is the “32_GPI2_PWM2” which is active low so “NOT 32_GPI2_PWM2” is when the signal is at a high voltage.

The blue signal shows a 12V output which is enabled from the output of the GPO from this LGPO configuration (12V_LD_SW).

The 32_GPI2_PWM2 is low for 4 seconds but based off the explanation of the GPO behavior when not ignoring inputs during delay, this should be ignored and shouldn’t cause 12V_LD_SW to go low. It should also be noted that the 12V_LD_SW goes low 9.8s after the 32_GPI_PWM2 went low.

So our expectation for the trace would be the blue trace, controlled by the GPO, would never go low because the input yellow trace does not stay low sufficiently long.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.