Other Parts Discussed in Thread: AM5716

I’ve been struggling with meeting the power-down sequence requirements in the TPS65916 data sheet, SLVSD09C, pg 75. The figure there describes it well:

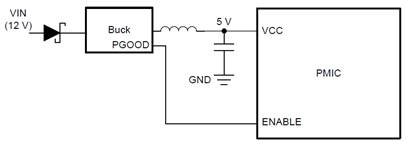

The intent is clear – just need to initiate the “ACTIVE to OFF” sequence a few milliseconds before VCC falls below ~2.8V. Creating the PGOOD signal is simple, but what to use for the PMIC “ENABLE” pin is the mystery. Presumably, one of the “OFF Requests” from table 5-3 would work, but I’ve eliminated them one-by-one for various reasons:

- PWRON pin: requires long assertion to cause OFF requeset (‘long press key’ = 4s minimum).

- PWRDOWN: not available, using GPIO_0 as REGEN1.

- RESET_IN: not available, using GPIO_1 as NRESWARM.

- VSYS_LO: Artificially pull VCCA low just enough to trigger OFF request, but not cause instant shutdown? Is this possible?

- POWERHOLD: Planning to use this for Power-On Acknowledge per section 5.3.5.

- GPADC_SHUTDOWN: Requires SW to set up OFF request trigger from adc input. (remaining four OFF Requests are not HW accessible)

Am I overlooking something? Is there a recommended way of triggering the power-down sequence with no (or minimal) SW setup?

By the way, our product will have no power switch, and no power-off or standby function. If it’s plugged in, it runs.

Thanks,

Nick