TPS62140A was occur EOS much for failure, please let me confirm about TPS62140A specification below;

①About TPS62140A and the same series, these device occur possibility of EOS for EN: High→Low on heavy load condition.

・Please let me know about threshold of "Heavy" Load.

・Is light load certainly not occur EOS?

・Is there any measure EOS for additional circuit?

②If there any correction point or confirm point for below circuit, please let me know.

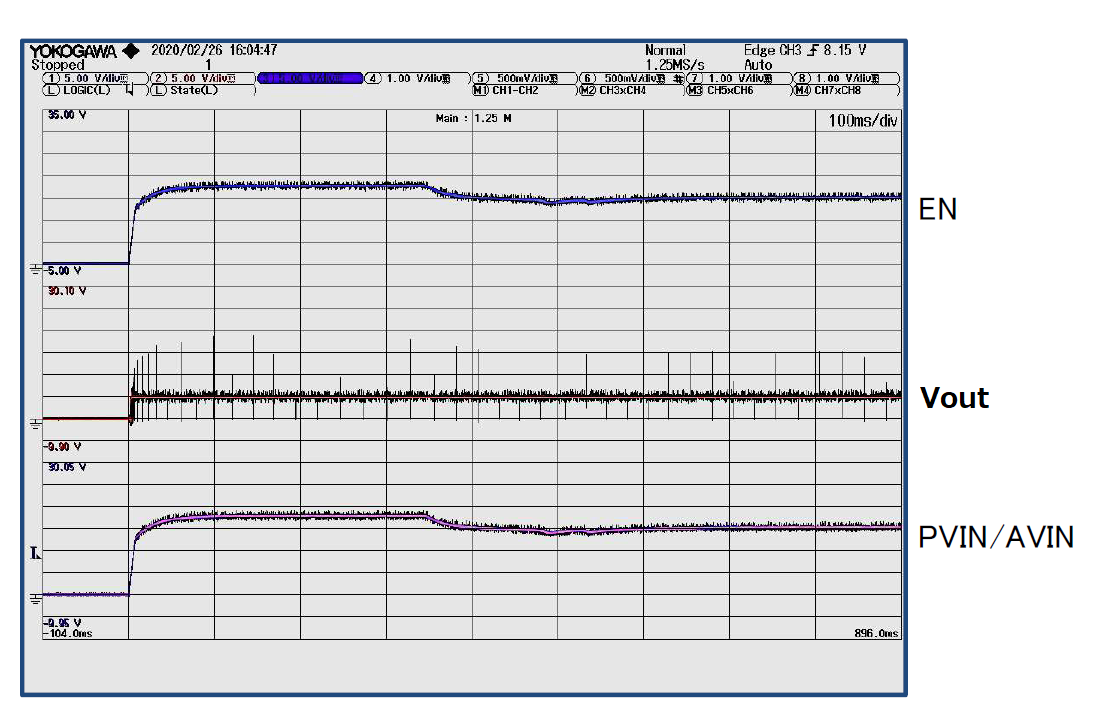

Schematic and waveform, layout is attached below;

(I think that schematic was not find mistake)

Best regards,

Satoshi