Other Parts Discussed in Thread: LP5562, LP8556, TUSB544,

We have some questions about I2C timing requirements defined in BQ2573A data sheet. (Rev. A, May 2018)

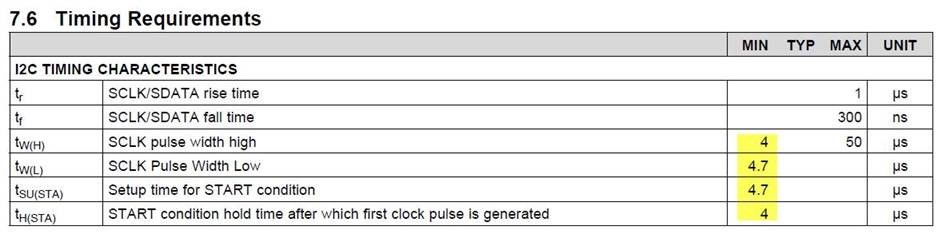

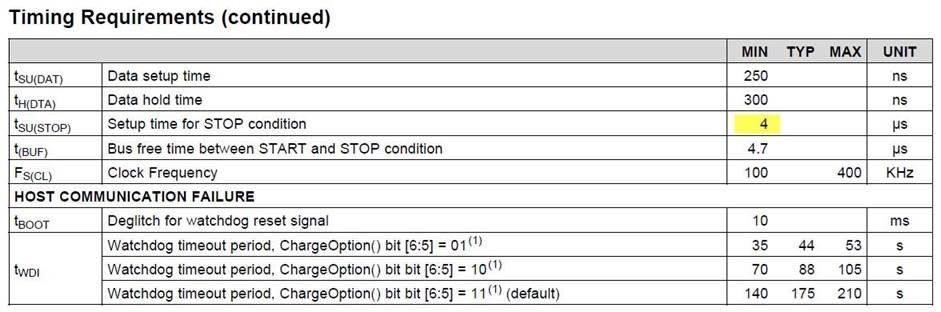

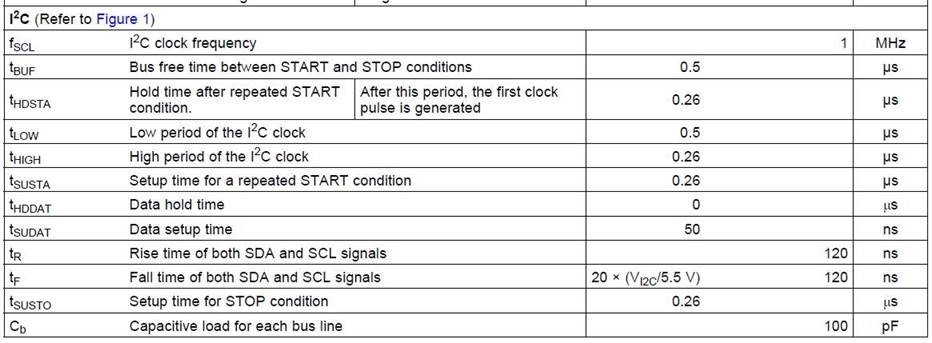

Here are the requirements.

Since these marked items are too long, we can’t fulfill them if I2C bus works over 100KHz.

For example, if I2C clock is 400KHz, its period is 2.5us, how does it pass these requirements?

They are also much larger than other I2C slave devices.

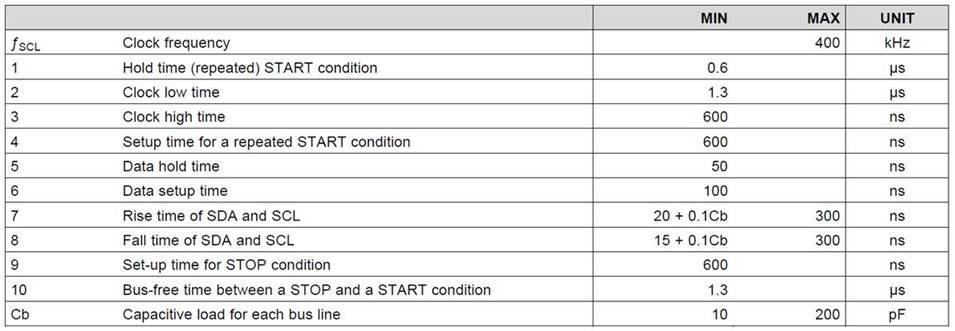

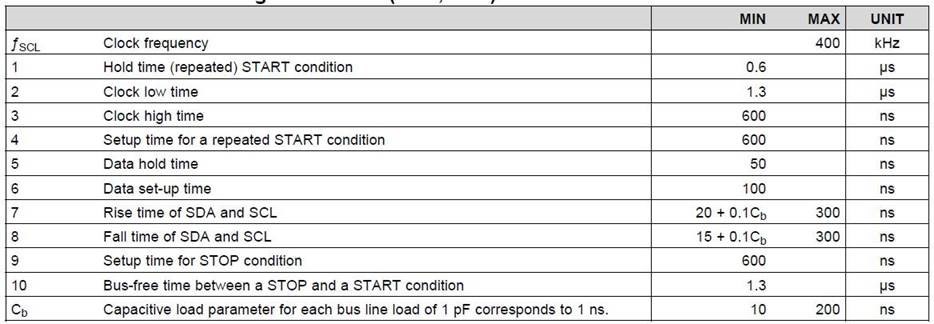

Here are three TI solutions.

LP5562:

LP8556:

TUSB544:

regards,

Mark