Other Parts Discussed in Thread: UCC27211, , TIDA-00364

hi

Non isolated gate drivers such as UCC27211 can handle –18 V on HS maximum for 100 ns .

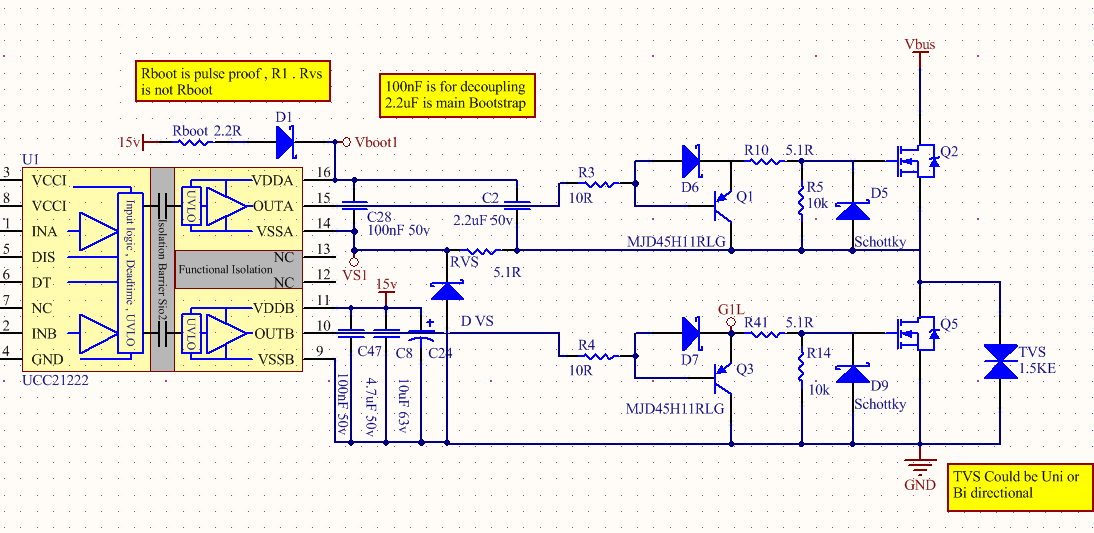

But what about isolated gate driver such as UCC21222 . when used in half bridge configuration for motor drivers (Vbus<100v).

My thought is that since there is no mention in the data sheet for the abs max rating for this pin ( VssA to VssB) . maybe it doesnot have limitation ??

1. Can you confirm my conclusion?

2. if Correct , then I should not care about reducing switch node ringing , right ?