Other Parts Discussed in Thread: TINA-TI

Dear *,

we are looking at the TLV62569A and output capacitor , we see that there are some recommended COUT values.

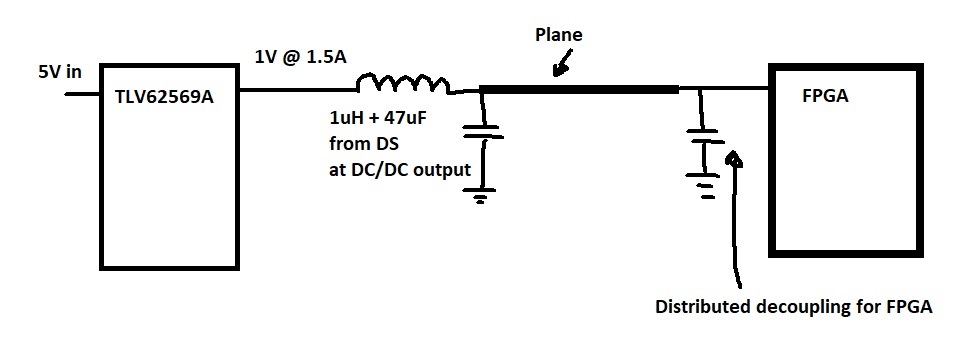

If we want to power FPGA core voltage with this device, the FPGA core has some distributed decoupling capacitance aground the FPGA ( Eg. 10x100nF + 5x10uF + 2x100uF ~ 250uF to 300uF),

the TLV62569A is 10cm away from FPGA and with a plane connected to the fpga rail.

1) Do you see any problem regarding load transient or instability for this configuration?

2) Because the effective Cout is more than 47uF, or is the 22uF-47uF from DS minimal value?

3) what is the negative impact of this much capacitance?

4) if we add a cff will this make a difference?

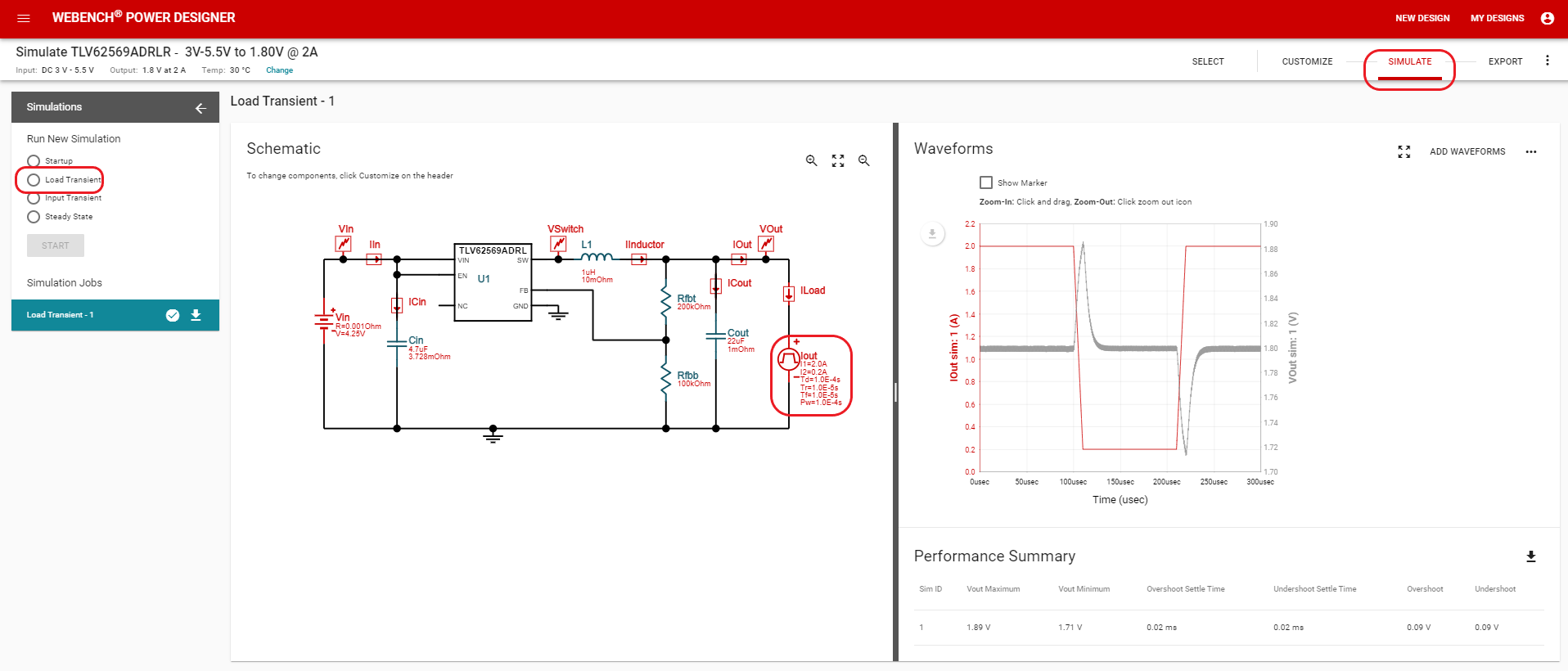

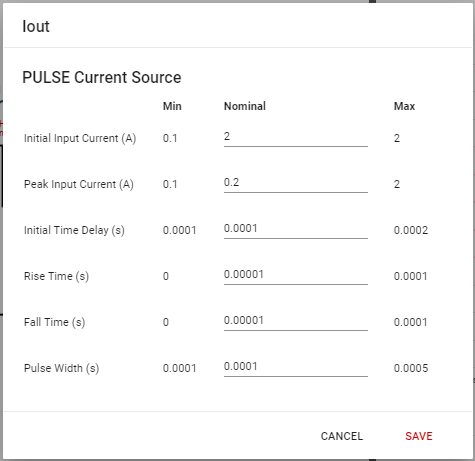

Is it possible and how to simulate this with WEBENCH?

Best Regards,.