Other Parts Discussed in Thread: TPS565208

Hi Team,

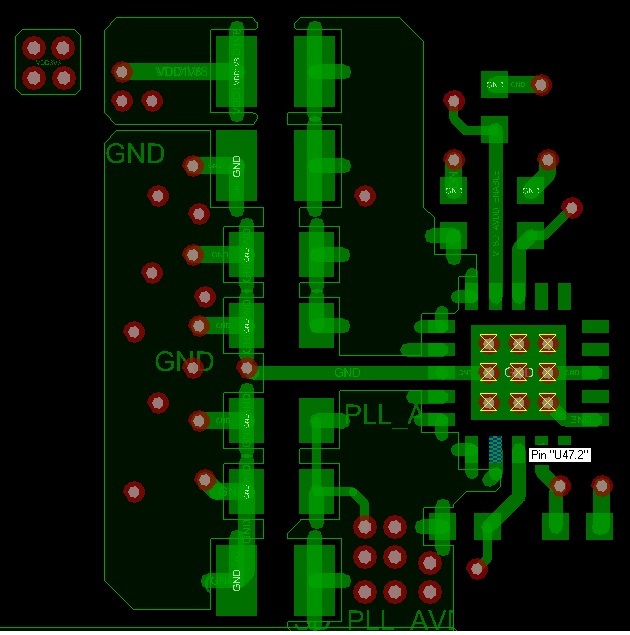

Attached is a schematic of my system design. VDD1V8 is converted from TPS565208.

The criteria of SD_PLL_AVDD1 output voltage ripple noise is 1.2mVp-p at 600KHz-20MHz bandwidth.

I have modified the C337(Cff) to 100nF, but it does not work. Do you have any suggestions? Thank you.

Muhsiu.