Other Parts Discussed in Thread: HALCOGEN

We are experiencing problems with the communication between a Hercules RM48 and a TPS65381A-Q1 when configuring the TPS65381A-Q1 after startup.

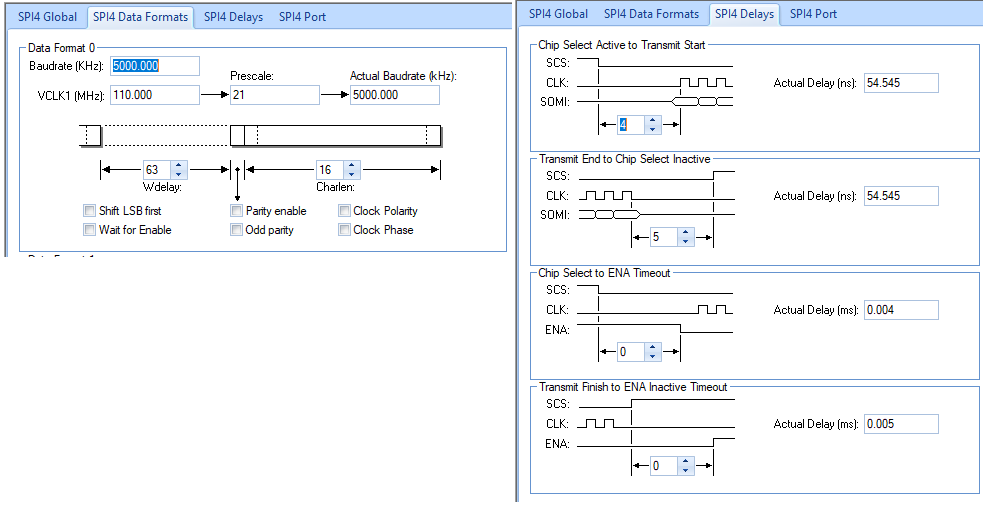

HALCoGen is used to configure SPI4. Our initial setting was:

With this configuration the communication works, but we do not meet the minimal value of t_hlcs 788 us as specified by SLVSDJ1A.

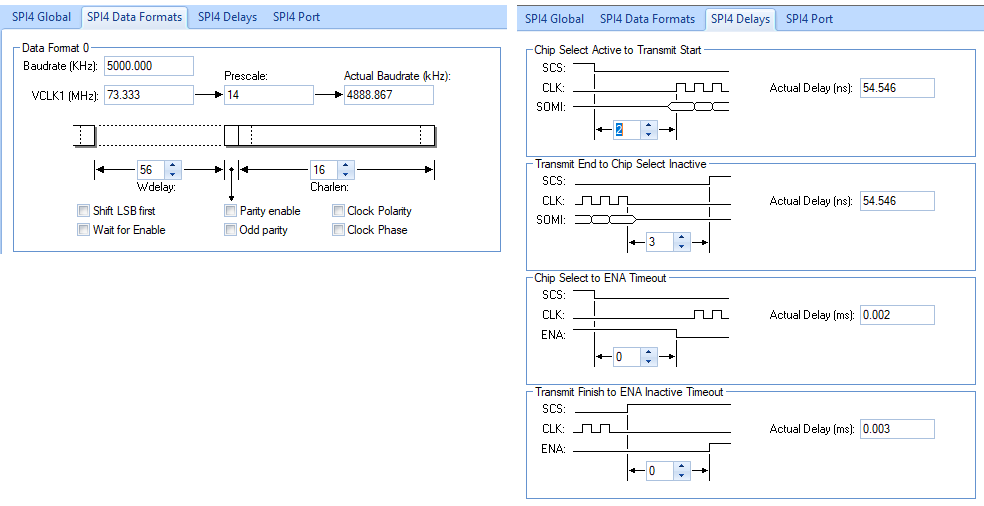

Therefore we changed the configuration to this:

We verified with a logic analyser that the SPI timing is still good, but the TPS65381A-Q1 seems to jump to safe state, instead of staying in diagnostic state during initialisation.

Do you have any suggestions what might be the cause of this behaviour, as I cannot see any relevant changes caused by the changed configuration?