Other Parts Discussed in Thread: TINA-TI

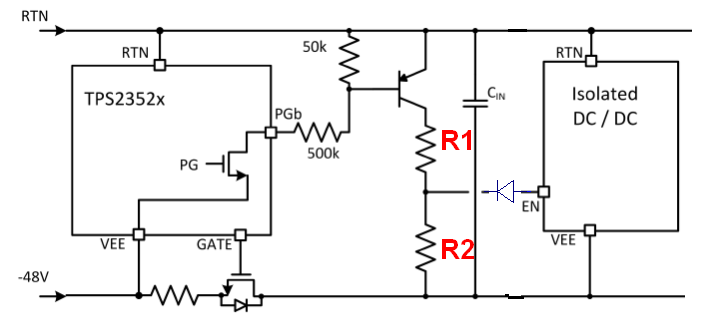

Hi, we've done a design based on the spec (9.2.2.10 Power Good Interface to Downstream DC/DC) to deactivate the downstream brick of the design.

However, we needed to tweak it a bit to get it work because we need to invert the PGb signal.

Here is what my design should have :

Hotswap GOOD

PGb = 0 Brick Enable pin = open

Hotswap NOT OK

PGb = Open Brick Enable pin = 0

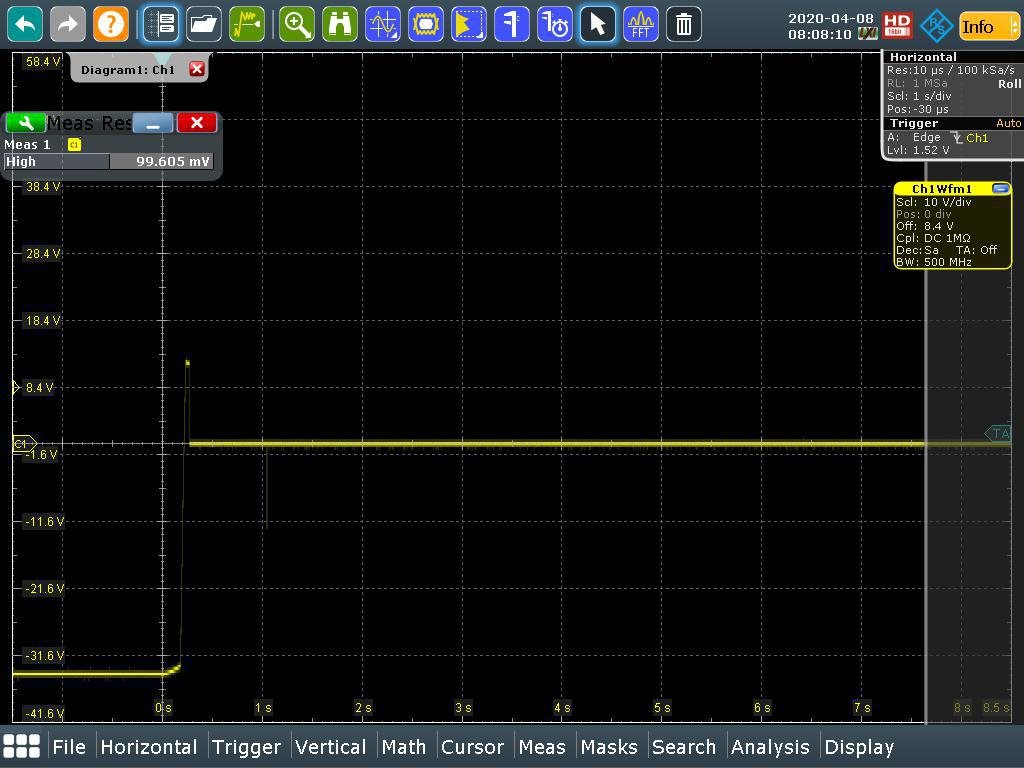

On my design the issue I just found is that the voltage divider at VEE is not working when PGb is floating because VEE became floating also because of the oring-FET!

By comparison with the hotswap spec (9.2.2.10 Power Good Interface to Downstream DC/DC) , on my design I also have an o-ringFET on the left…which disconnect VEE so the voltage divider is no longer working between RTN and VEE…My FET is then having 48V at his gate which failed the Vgs spec of 20V and burn it I guess…

Does we can use another pin as a references to do that? like Vref or something else?

Or any other idea?

Thanks for your help!

David