Other Parts Discussed in Thread: UCC21732,

Hi Team,

UCC21750 was also used in customer for Traction inverter, and it has some issue. Could you help us on that? Thanks.

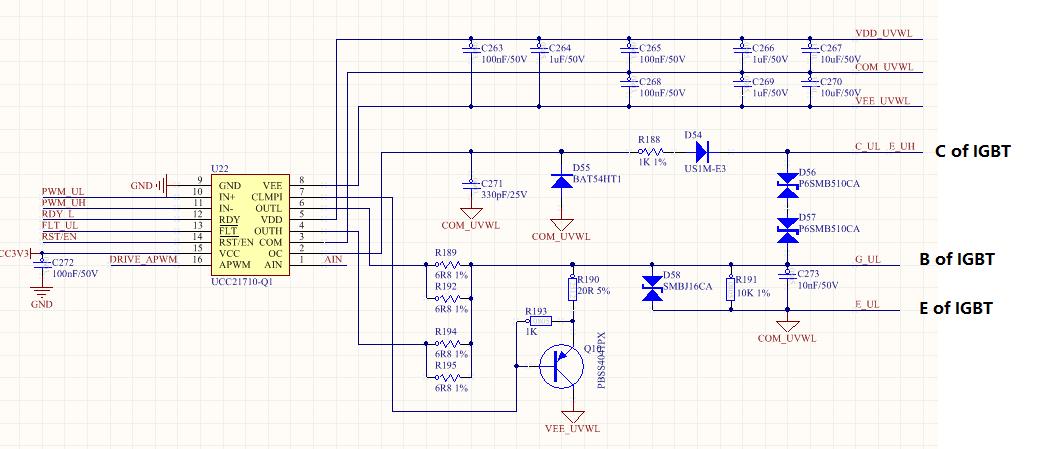

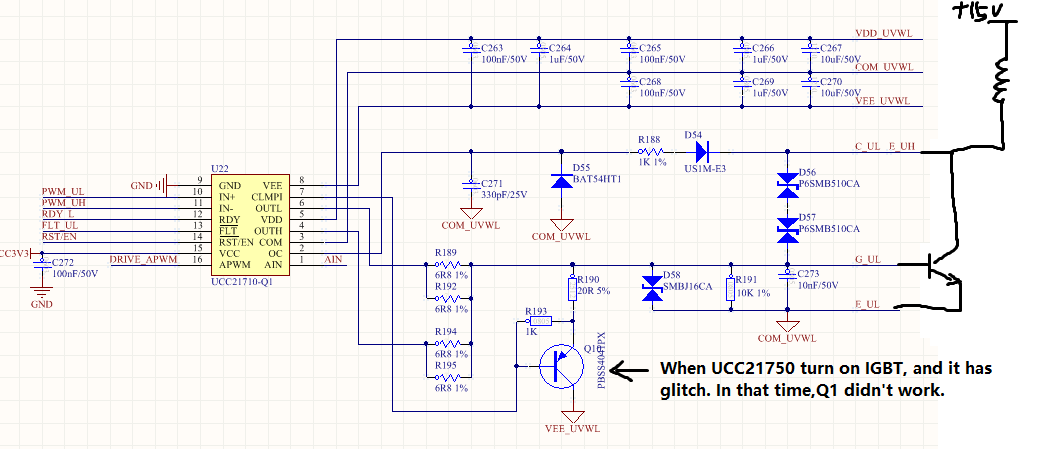

Here is the schematic from customer:

Test Condition:

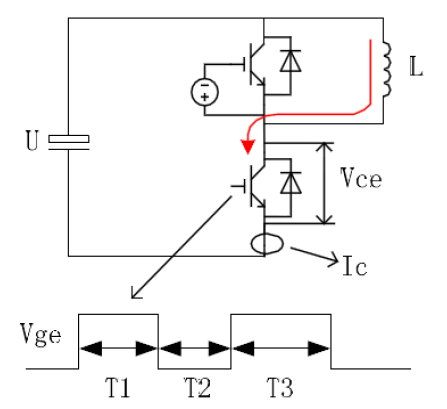

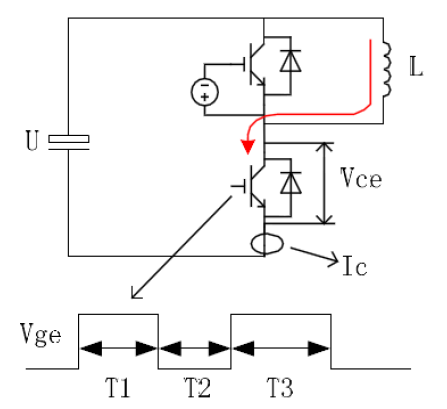

A external inductor was paralleled on high side IGBT, it shows in figure 1;

Issue:

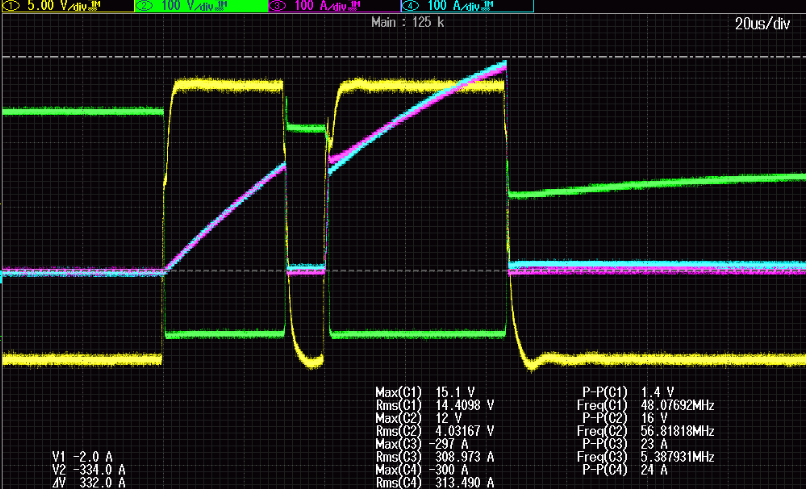

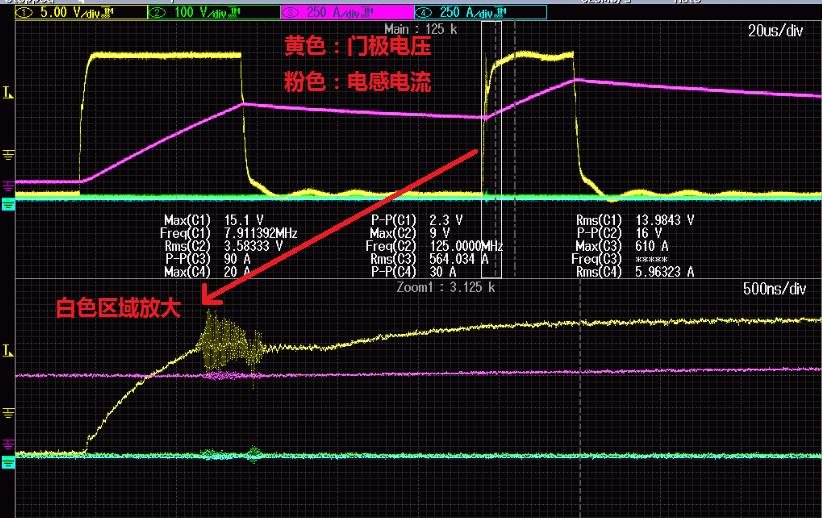

When customer used the trigger waveform to drive IGBT, it work well in T1 and T3 for the first time, it shows in figure2;

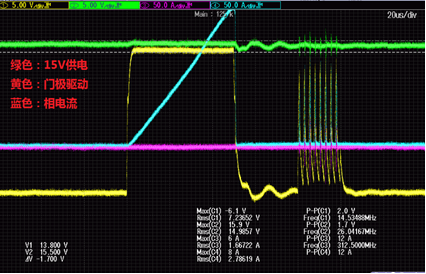

but when customer use the same waveform to trigger the IGBT for second time, it have lots of glitch in OUTH(PIN 4). It shows in figure 3.

Figure 1 Test Condition

Figure 2( Yellow for OUTH, Green for OC(pin2), Pink and blue for current in IGBT)

Figure 3( Yellow for OUTH, Green for OC(pin2), Green for 15V power of IGBT, blue for current in IGBT)

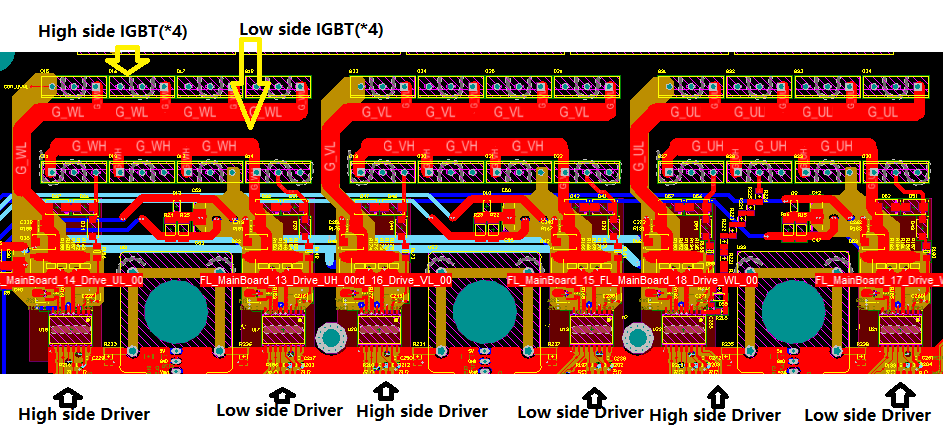

Information about IGBT

BR

Songzhen Guo